UNIVERSITY OF GRONINGEN

FINAL BACHELOR DEGREE PROJECT

---

# Properties and Neuromorphic Applications of Co/Nb:STO based Memristors

Computing Beyond von Neumann

---

*Author:*

Jacobo GÓMEZ (s5156491)

*Examiners*

Prof. Dr. Ir. Tamalika Banerjee

Prof. Dr. Ir. Caspar van der Wal

JUNE 27, 2025

*Daily Supervisor:*

Himanshu Rai

## Abstract

### **The Role of Co/Nb-doped SrTiO<sub>3</sub> in Neuromorphic Computing**

Neuromorphic computing aims to fabricate memory devices capable of mimicking the structure of neurons and synaptic connections in the brain.

This approach allows for the co-localization of memory and information processing functionalities, overcoming the efficiency limitations of traditional computing associated with the von Neumann bottleneck and the slowdown of Moore's Law. The objective of this research was to fabricate and study the electrical properties of Cobalt and Niobium-doped Strontium Titanate (Co/Nb:SrTiO<sub>3</sub>) junctions with interface-based memristive properties, and

to discuss their role as embedded-memory systems in the context of neuromorphic computing. To this end, the devices were fabricated using electron beam lithography techniques and electrically characterized using the Keysight B1500A Semiconductor Device Analyze. The results show that the fabricated Co/Nb:SrTiO<sub>3</sub> devices exhibit low device-to-device variation, the ability to enhance their capabilities when miniaturized, non-binary memory states, and the capacity to modulate their conductance through current potentiation and depression. All these conditions are highly beneficial for neuromorphic applications and the development of biological sensors. However, certain limitations related to response speed and destructive readout of states require further investigation.

# Contents

|                                                                   |    |

|-------------------------------------------------------------------|----|

| Abstract                                                          | 1  |

| List of Figures                                                   | 3  |

| 1 Introduction                                                    | 4  |

| 1.1 Background . . . . .                                          | 4  |

| 1.2 Memristors . . . . .                                          | 5  |

| 1.3 Nb-doped SrTiO <sub>3</sub> . . . . .                         | 6  |

| 1.4 Scope and Structure . . . . .                                 | 8  |

| 2 Theoretical Background                                          | 10 |

| 2.1 Schottky Barrier Formation . . . . .                          | 10 |

| 2.2 Schottky Barrier Under Bias . . . . .                         | 11 |

| 2.3 Carrier Transport . . . . .                                   | 13 |

| 2.3.1 Thermionic Emission . . . . .                               | 13 |

| 2.3.2 Tunneling . . . . .                                         | 14 |

| 2.3.3 Resistive Switching by Trap Assisted Tunneling . . . . .    | 15 |

| 3 Methodology                                                     | 17 |

| 3.1 Device Fabrication . . . . .                                  | 17 |

| 3.1.1 Sample Preparation . . . . .                                | 17 |

| 3.1.2 Experimental Procedure . . . . .                            | 19 |

| 3.2 Electrical Characterization . . . . .                         | 22 |

| 4 Results and Discussion                                          | 23 |

| 4.1 Current-Voltage Characteristics . . . . .                     | 23 |

| 4.2 Device Scaling Effects . . . . .                              | 24 |

| 4.3 RESET and SET Voltage Variations . . . . .                    | 25 |

| 4.4 Resistance Changing Rate at Constant Voltage Pulses . . . . . | 26 |

| 4.5 Potentiation and Depression Behaviour . . . . .               | 29 |

| 4.6 Discussion . . . . .                                          | 30 |

| 4.7 Experimental and Theoretical Limitations . . . . .            | 32 |

| 5 Conclusion                                                      | 33 |

| Acknowledgements                                                  | 35 |

| Bibliography                                                      | 38 |

| A Electrical Measurements Modes                                   | 39 |

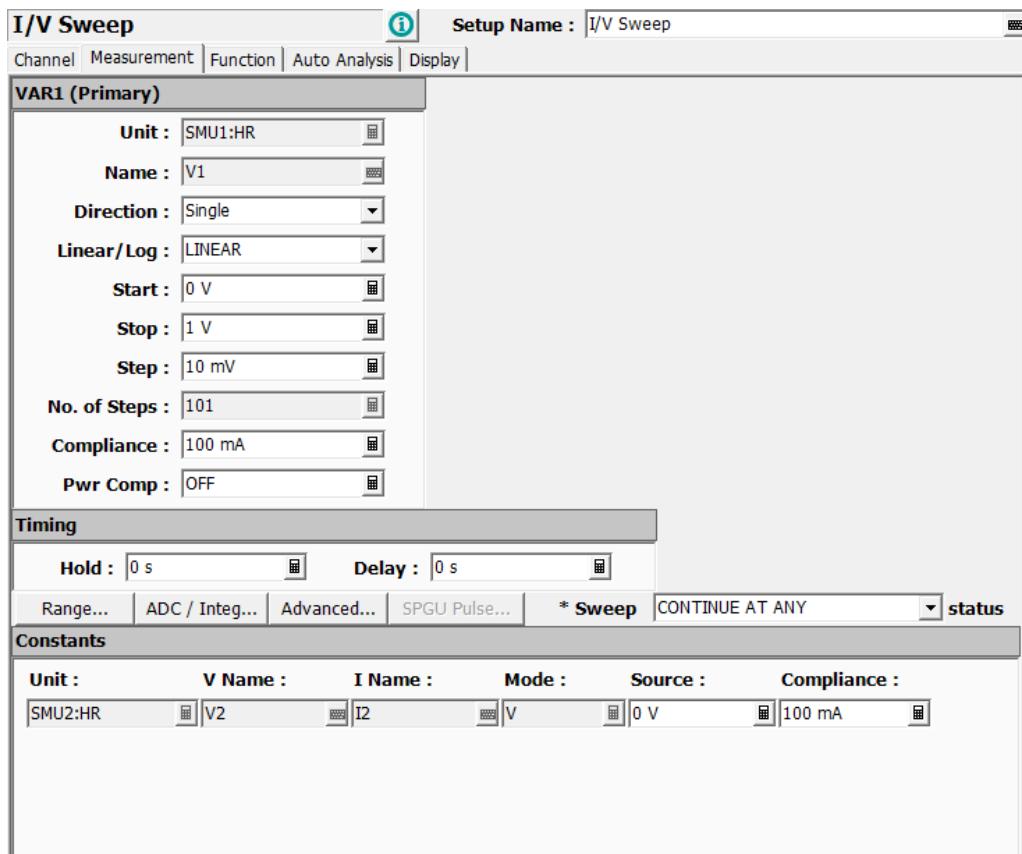

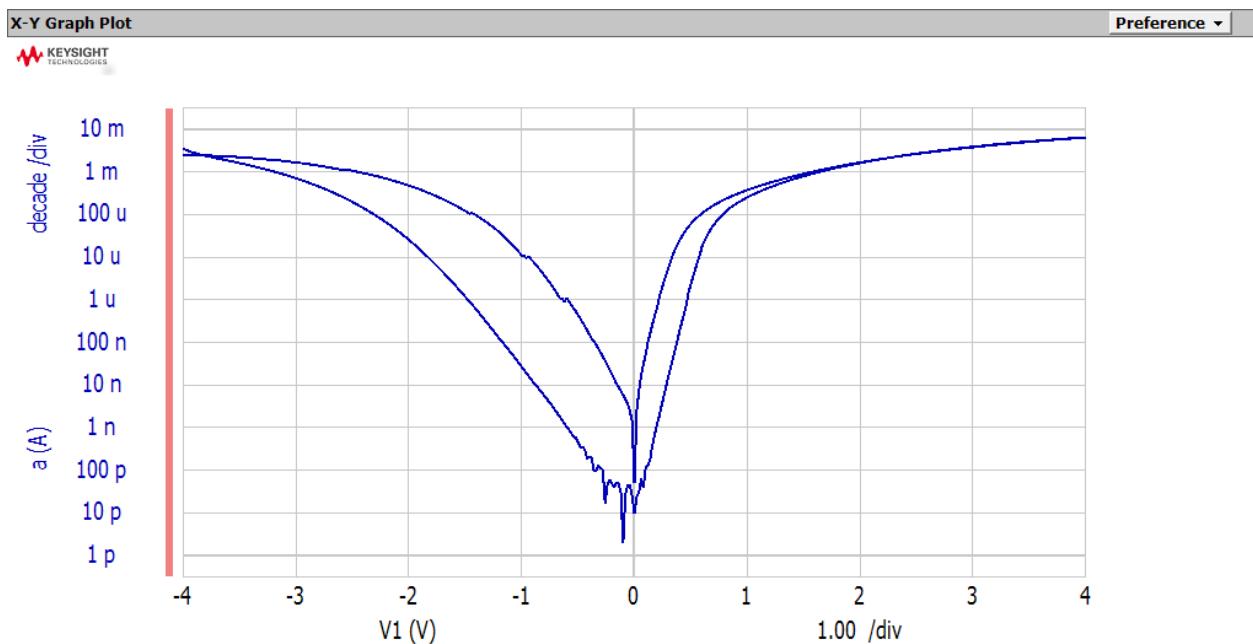

| A.1 I/V Sweep Test . . . . .                                      | 39 |

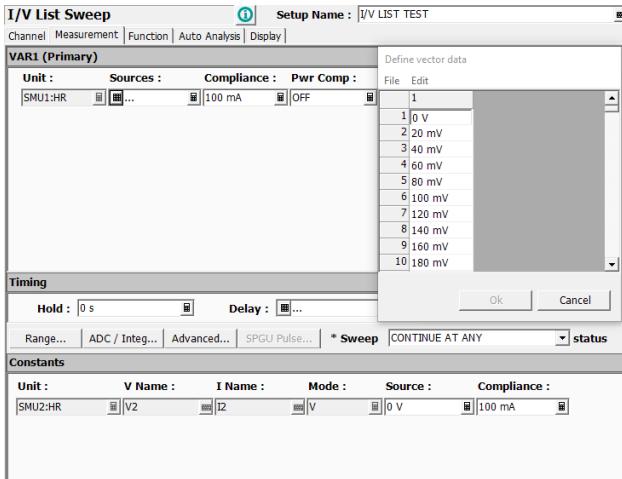

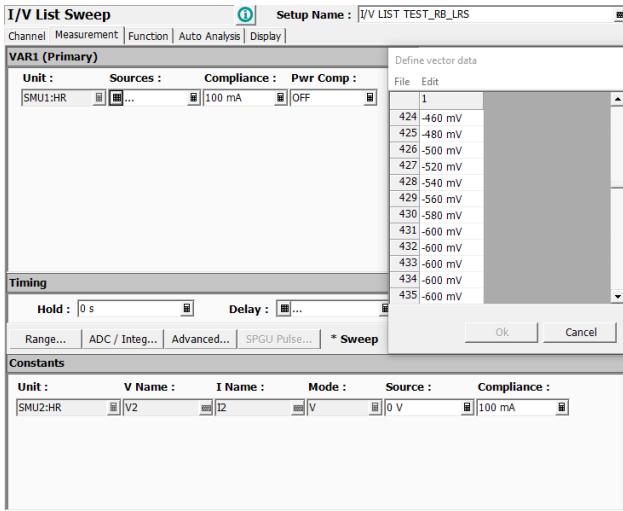

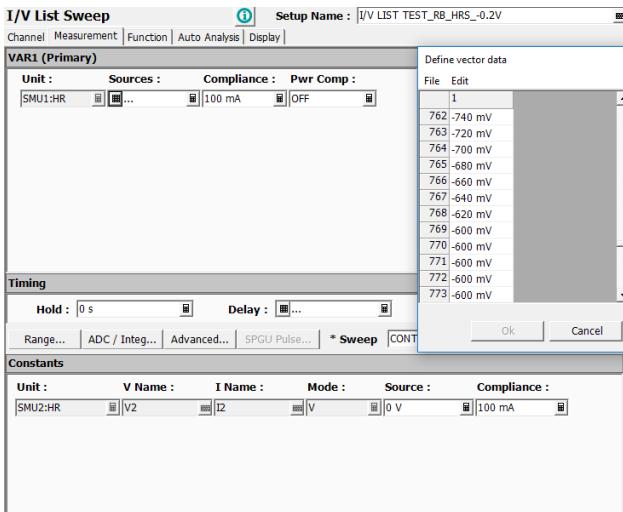

| A.2 I/V List Test . . . . .                                       | 41 |

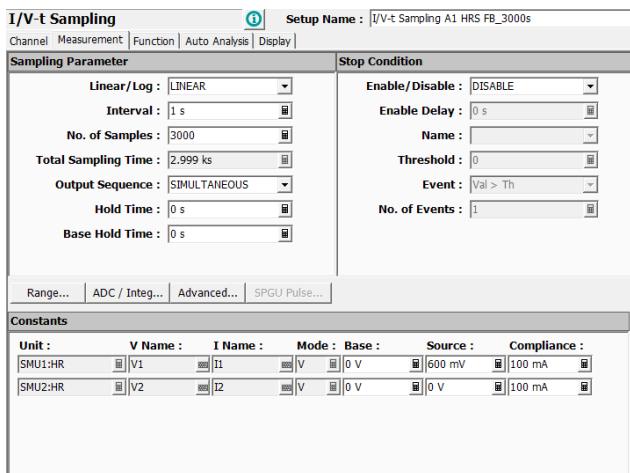

| A.3 I/V-t Sample . . . . .                                        | 43 |

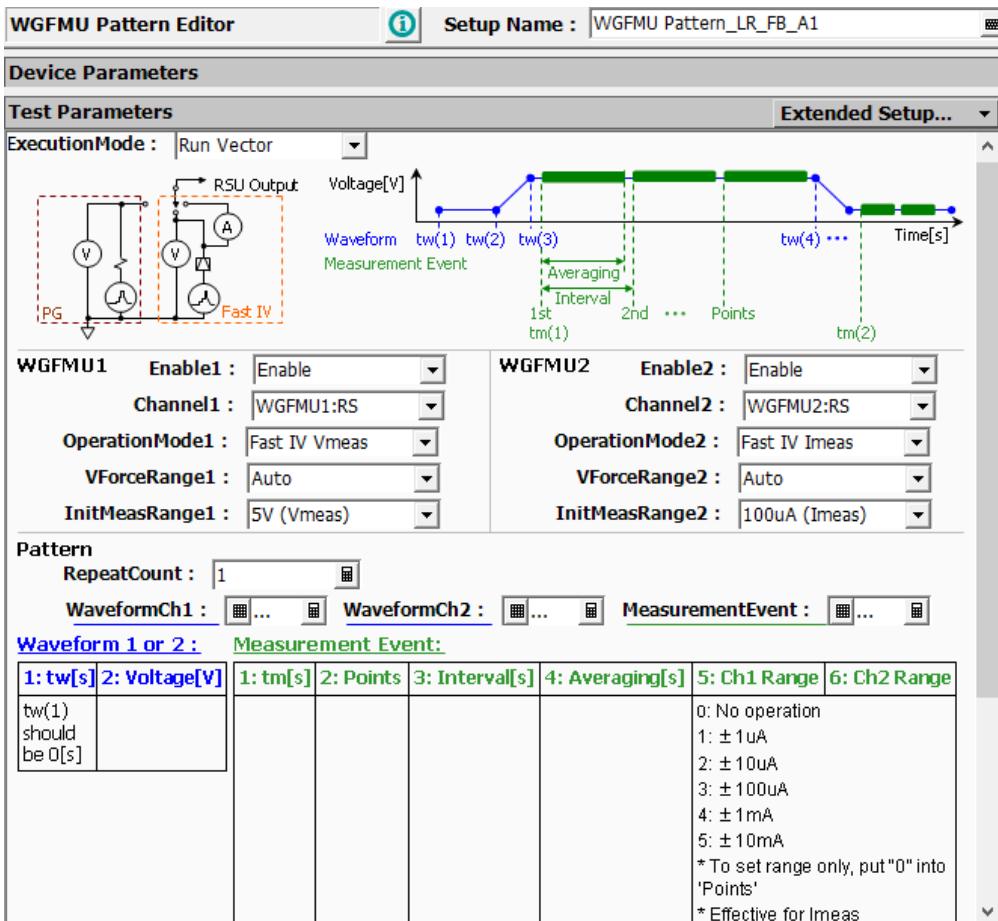

| A.4 WGFMU . . . . .                                               | 44 |

| A.4.1 Channel Configuration . . . . .                             | 44 |

| A.4.2 Pattern Configuration . . . . .                             | 44 |

---

|     |                                                       |    |

|-----|-------------------------------------------------------|----|

| B   | Supplementary Plots                                   | 48 |

| B.1 | Resistance Time Dependence at Constant Voltage Pulses | 48 |

| B.2 | Time Range Measurements                               | 50 |

# List of Figures

|                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1.1 The four fundamental circuit elements . . . . .                                                                                                                           | 5  |

| 1.2.1 Typical I/V characteristics of a memristor . . . . .                                                                                                                      | 6  |

| 1.3.1 Three dimensional cubic lattice of SrTiO <sub>3</sub> . . . . .                                                                                                           | 7  |

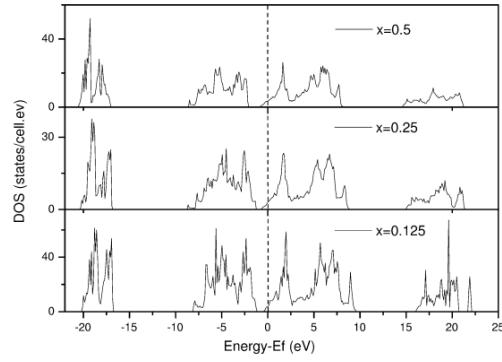

| 1.3.2 Comparison of the Density of States of SrTiO <sub>3</sub> and Nb:SrTiO <sub>3</sub> for different doping concentrations [36]. . . . .                                     | 8  |

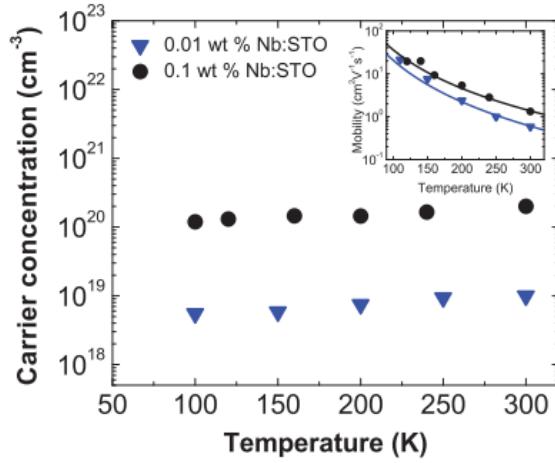

| 1.3.3 Temperature dependence of carrier concentration and mobility for 0.01 and 0.1 wt % Nb doped SrTiO <sub>3</sub> in the temperature range from 100 K to 300 K [30]. . . . . | 9  |

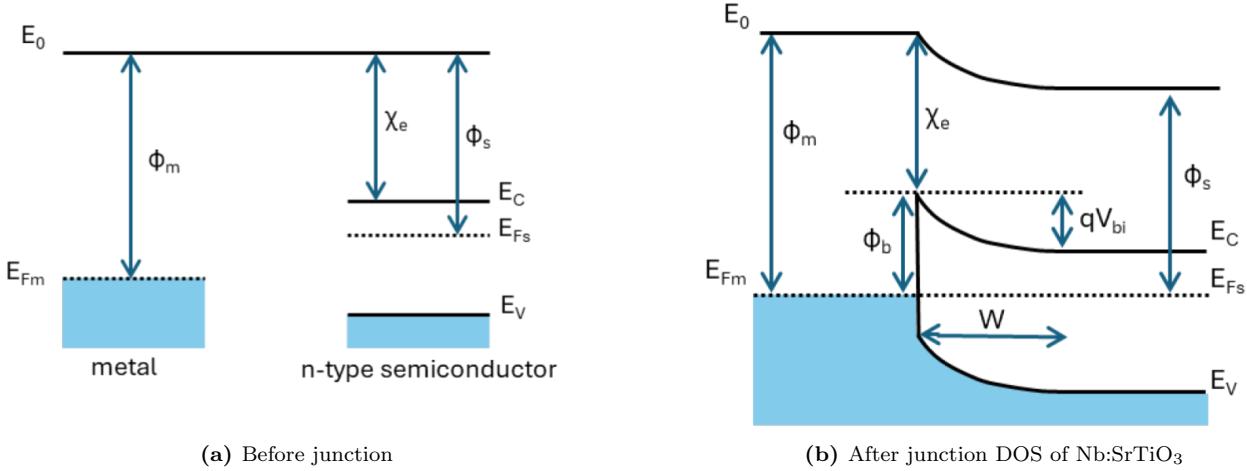

| 2.1.1 Energy band diagram of a metal and an n-type semiconductor junction before and after contact. . . . .                                                                     | 11 |

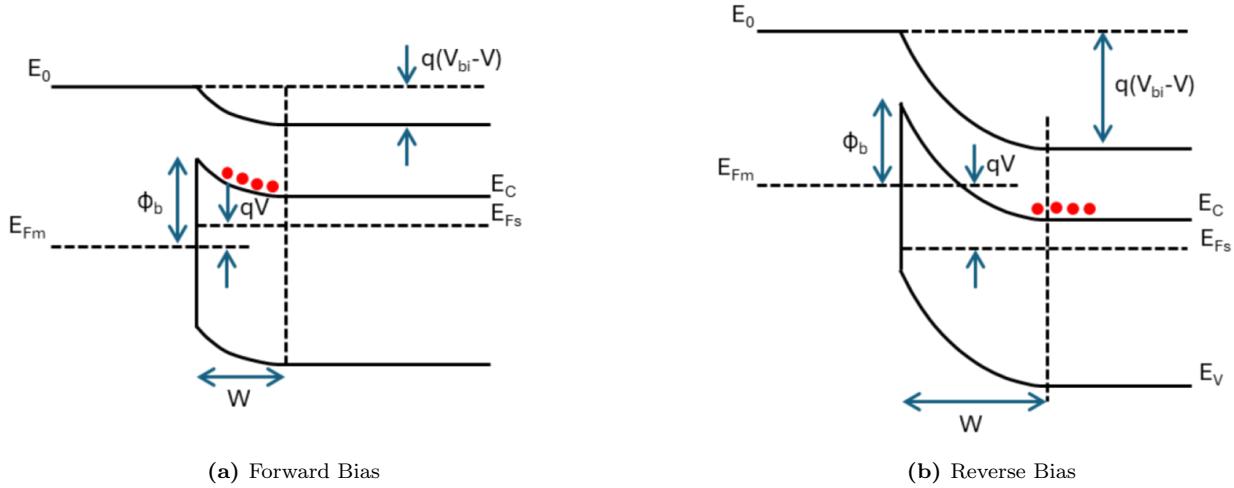

| 2.2.1 Energy band diagram of a Schottky contact under forward and reverse bias. . . . .                                                                                         | 12 |

| 2.2.2 Diagram of the carrier transport mechanisms . . . . .                                                                                                                     | 13 |

| 2.3.1 Interfacial layer and trapping states in non-ideal Schottky contact. . . . .                                                                                              | 15 |

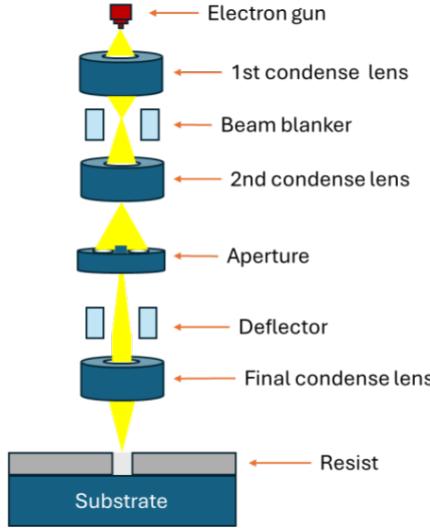

| 3.1.1 Typical structure of the optical column of an Electron Beam Lithography machine. . . . .                                                                                  | 18 |

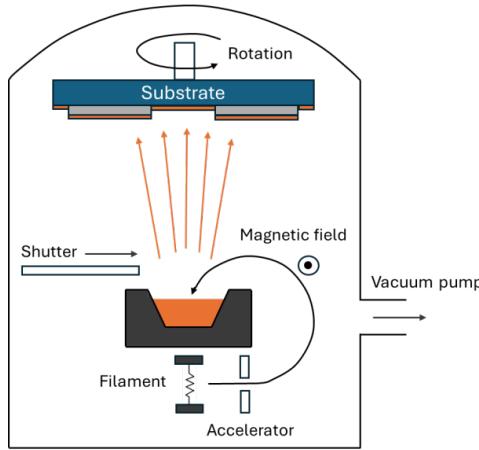

| 3.1.2 General setup of an electron beam evaporation machine. . . . .                                                                                                            | 19 |

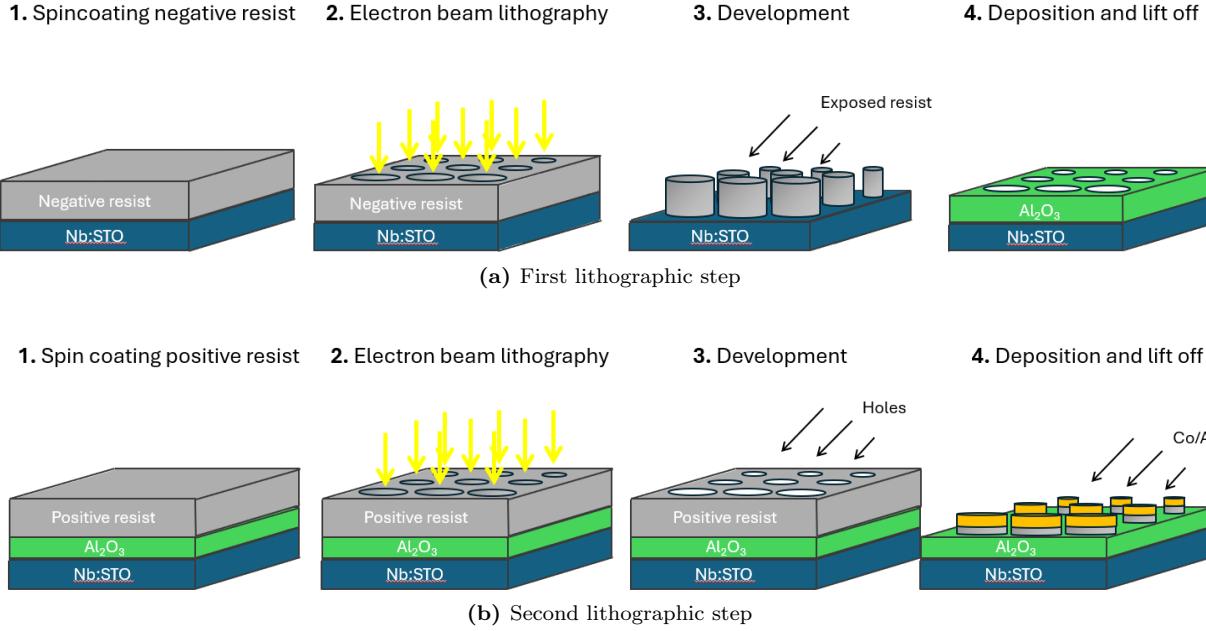

| 3.1.3 Steps of the fabrication process of Co/Nb:SrTiO <sub>3</sub> memristive contacts. . . . .                                                                                 | 20 |

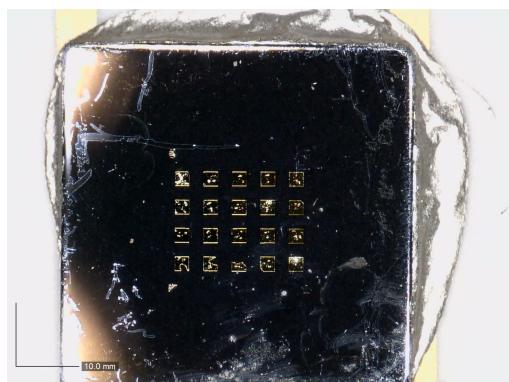

| 3.1.4 Disposition of the fabricated devices in the measuring chip. . . . .                                                                                                      | 21 |

| 3.1.5 Experimental setup for the electrical characterization of samples using the B1500A Keysight Analyzer [10] . . . . .                                                       | 22 |

| 4.1.1 Current-voltage characteristics of several equal-sized devices. . . . .                                                                                                   | 24 |

| 4.2.1 Current-voltage characteristics of devices with different sizes from 800 nm to 300 nm . . . . .                                                                           | 25 |

| 4.3.1 Current-voltage characteristics of a device under voltage sweeps with different ranges. . . . .                                                                           | 26 |

| 4.4.1 Resulting current at constant reading voltage pulses for each state . . . . .                                                                                             | 27 |

| 4.4.2 Comparison of currents from HRS and LRS of forward and reverse under constant reading voltage pulses. . . . .                                                             | 28 |

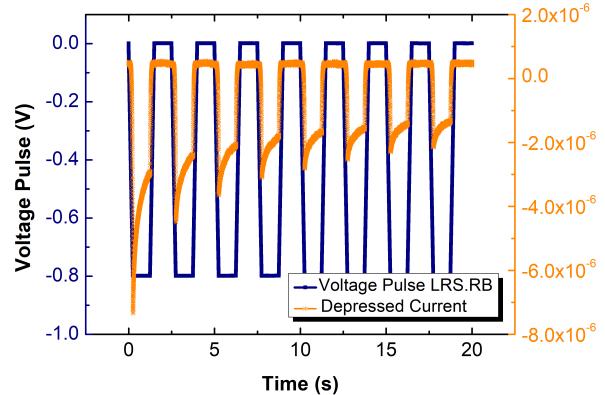

| 4.4.3 Potentiation and depression characteristics due to numerous identical voltage pulses. . . . .                                                                             | 29 |

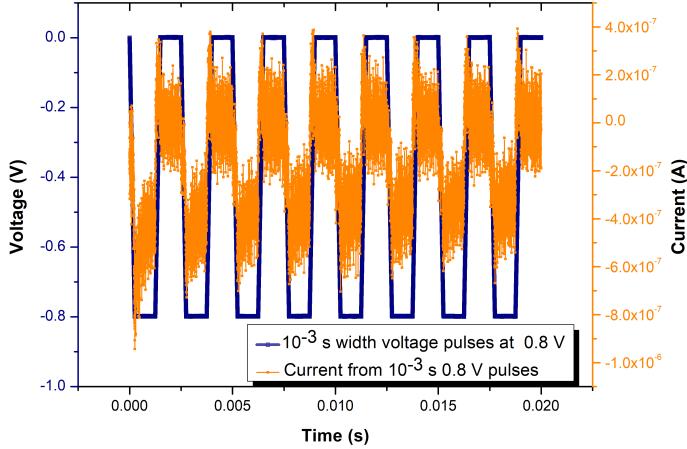

| 4.5.1 Depressive behaviour in the milisecond time range . . . . .                                                                                                               | 30 |

| A.1.1 Measurement configuration in I/V Sweep Test mode. . . . .                                                                                                                 | 40 |

| A.1.2 I/V Sweep example of measurement. . . . .                                                                                                                                 | 40 |

| A.2.1 I/V sweep measurement made using the I/V List Test. . . . .                                                                                                               | 41 |

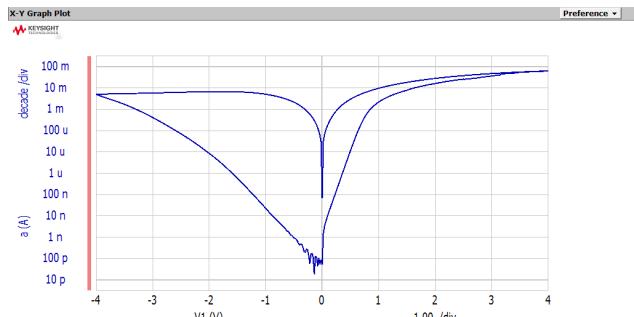

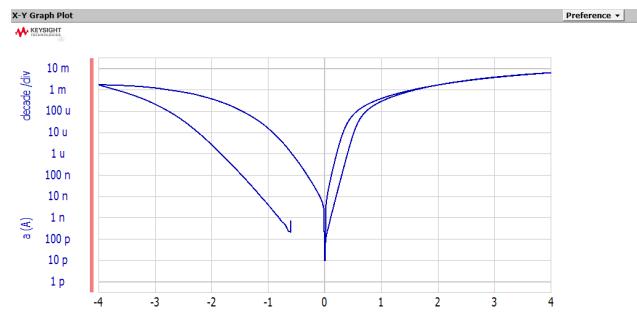

| A.2.2 Example of I/V List Test measurement in LRS of reverse bias. . . . .                                                                                                      | 42 |

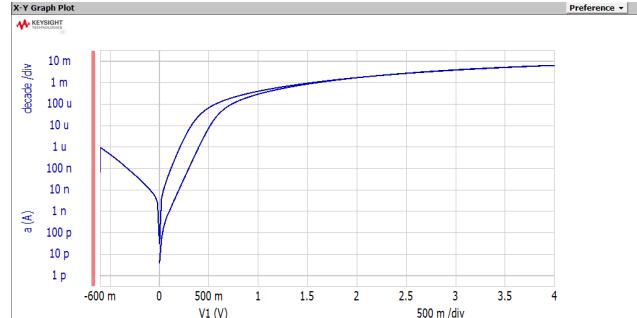

| A.2.3 Example of I/V List Test measurement in HRS of reverse bias. . . . .                                                                                                      | 42 |

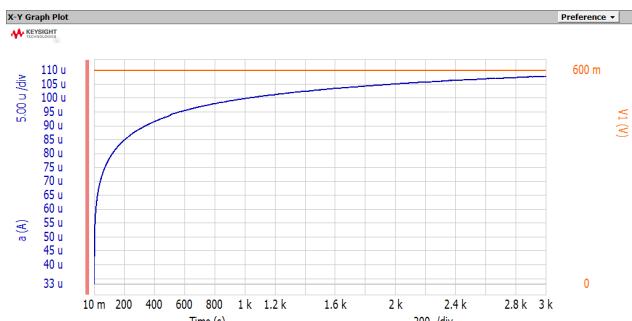

| A.3.1 Example of I/V List Test measurement in HRS of reverse bias. . . . .                                                                                                      | 43 |

| A.4.1 Measurement configuration in WGFMU mode. . . . .                                                                                                                          | 45 |

| A.4.2 Waveform channels configuration . . . . .                                                                                                                                 | 46 |

| A.4.3 Measuring events configuration. . . . .                                                                                                                                   | 46 |

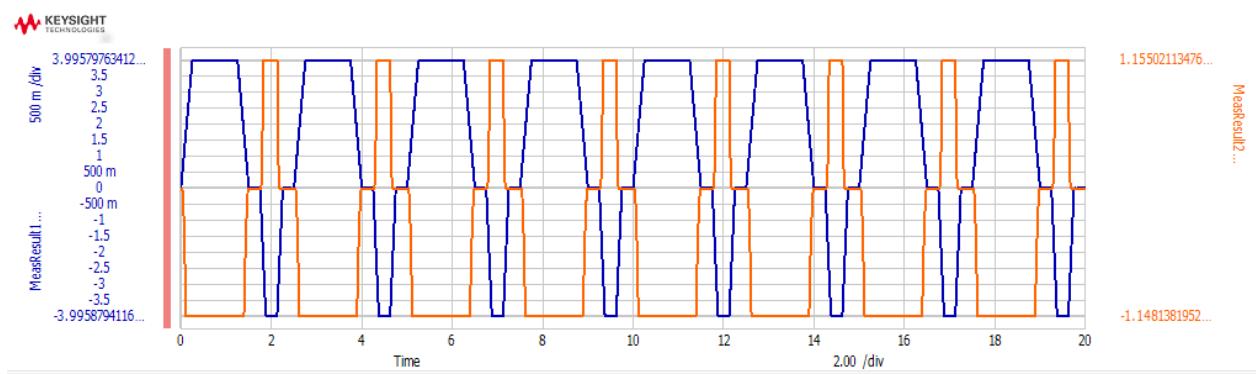

| A.4.4 Writing voltage pulse and output current measured with the WGFMU mode. . . . .                                                                                            | 47 |

| B.1.1 Resistance changes in the current at constant voltage in every state using the I/V List Test. .                                                                           | 48 |

| B.1.2 Writing voltage pulses to access every state before applying a constant voltage. . . . .                                                                                  | 49 |

| B.2.1 Time range . . . . .                                                                                                                                                      | 50 |

# Chapter 1      Introduction

## 1.1 Background

The von Neumann architecture has proven to be highly significant as the main paradigm of traditional computing since its conceptualization in the mid-20th century [21]. This structure was designed with the purpose of storing both data and program instructions within the same memory space [26]. In this way, both types of information could be written in binary code, allowing the computer to process them efficiently without the need for manual hardware modifications. The simplicity, speed, and versatility of this architecture have led to its widespread adoption in all commercial computers from its initial implementation to the present day.

Nevertheless, the constant demand for the evolution and improvement of computing devices has highlighted the inherent inefficiencies of this type of architecture. In conventional computers, the components responsible for memory storage are physically separated from the central processing unit (CPU), which is in charge of interpreting, processing, and executing instructions encoded in software programs [7]. The fact that these two functions are virtually separated allows for data to be fetched and processed only in a sequential manner, requiring a mechanism capable of transferring information from memory to the CPU. This is achieved through buses, which provide a transmission channel to facilitate data transfer, but this comes at the cost of increased energy consumption. Moreover, processing speed is significantly lower compared to the rate at which data can be transferred from memory. This limits the overall throughput of the device, which could potentially deliver higher performance than it does due to the constraints imposed by its architecture [9], [22].

These limitations in energy and time efficiency are known as the von Neumann bottleneck, representing one of the main challenges to overcome in the context of modern computing. Additionally, the exponential reduction in the size of electronic components, as described by Moore's Law, is beginning to reach its limits. Several microprocessor manufacturers have stated that the miniaturization of CMOS-based transistors in a cost-effective manner is already slowing down, which means that performance improvements driven by size reduction will also significantly decline in the coming years [6].

In light of this situation, there is a growing need to develop a new computational paradigm capable of overcoming the limitations associated with the von Neumann bottleneck and the physical constraints of electronic component size. In this regard, neuromorphic computing emerges as one of the most promising options for the future of computing. This novel approach aims to replicate the operational principles of the human brain in terms of information storage, cognition, and processing. The structure of the brain provides memory functions through synaptic connections formed by an extensive neural network, while neurons are responsible for processing. In this way, both functions are co-located, allowing humans to manage large amounts of information in parallel, rapidly and with extremely low energy consumption [2], [27]).

Artificial neuromorphic systems aim to simulate neural networks with synaptic interconnections using memory devices and processors. In this context, new materials with potentially optimal properties are being investigated for their possible application in brain-inspired computing systems. Among these, memristors have emerged as particularly promising due to their unique characteristics, making them increasingly important components in neuromorphic architectures. In this research project, the properties of Nb-doped SrTiO<sub>3</sub> (Nb:STO), a doped oxide perovskite, are explored. To this end, various devices composed of Co/Nb:STO were tested, and their potential computational applications were discussed.

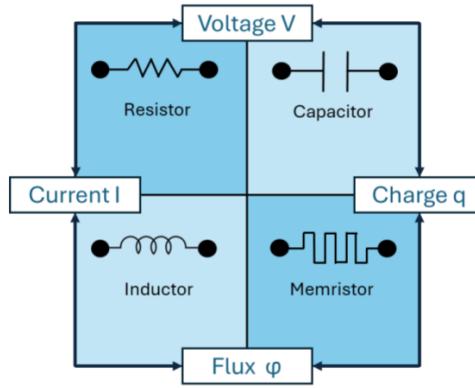

**Figure 1.1.1:** The four fundamental circuit elements

## 1.2 Memristors

Classical electronics is fundamentally built upon three basic passive components: the resistor (1827), the capacitor (1745), and the inductor (1831). Each of these elements is defined by its ability to relate the four fundamental electrical quantities: charge, current, voltage, and magnetic field [33]. These relationships are illustrated in Figure 1.1.1.

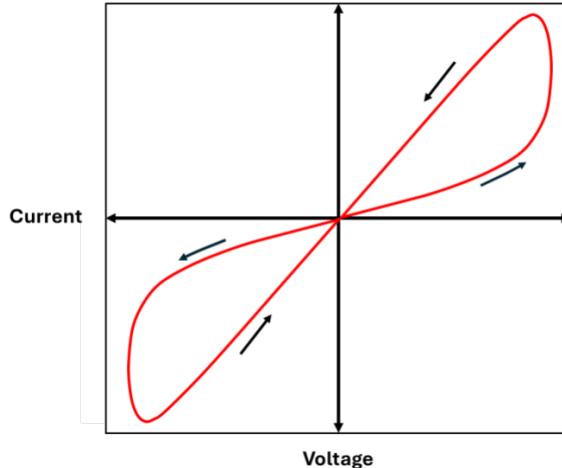

However, this definition is controversial because it was stated without experimental corroboration. Instead, since their first physical realization by HP Labs in 2007 [14], memristors are characterized by their ability to exhibit nonlinear resistance depending on the polarity, magnitude, and duration of the applied voltage. Based on these parameters, memristors can display different behaviors in terms of their opposition to electric current, alternating between various resistance states in a process known as resistive switching. The presence of these distinct states becomes evident in the typical I/V characteristic of memristors, where a pinched hysteretic current loop appears, featuring two distinct branches associated with each resistance state (see Figure 1.2.1) [5].

Although the exact physical phenomena involved in the resistive switching processes of memristors remain unknown, two main types can be distinguished based on the origin of the resistance state changes: unipolar and bipolar switching.

Thermal excitation plays a major role in the resistance state changes of non-conducting memristors with unipolar resistive switching, which are typically composed of two metal electrodes separated by a dielectric material [18]. Due to soft voltage breakdowns of the dielectric, small fragments of metal can be released and penetrate into the insulating material. This leads to the formation of conductive filaments that bridge both electrodes, thereby increasing the overall permittivity of the memristor. Through local Joule heating, oxygen ion migration, and Mott transitions, the formation of these filaments is facilitated, allowing the device to reach a lower resistance state (LRS). Once the LRS is set, the high resistance state (HRS) can be reset by destroying the conductive filaments, returning the device to more stable, lower thermal conditions. Thus, the resistance switching in unipolar memristors is reversible, although it has been observed that the resistance values do not return to those of the material's pristine state.

On the other hand, bipolar resistive switching occurs in oxide memristors connected to a metal electrode [5]. In this case, the primary factor influencing resistance state changes is the polarity of the applied voltage. These changes originate from local modifications in the interfacial layer structure between the two materials, which involve oxygen vacancy migration, major carrier transport, and, most importantly, the trapping and

**Figure 1.2.1:** Typical I/V characteristics of a memristor

detrapping of charges. All of these mechanisms are driven by electrical effects, which alter the potential barrier opposing current flow and can either facilitate (LRS) or hinder (HRS) the passage of current through the interface.

In this thesis, the memristive behavior of Co/Nb:STO is examined. Its structure is defined by the combination of a metal (Co) and a semiconducting oxide perovskite (Nb:STO). Consequently, the dominant mechanism behind the resistance state transitions in this device is bipolar resistive switching, resulting from structural changes at the formed interface. The growing interest in this material for neuromorphic computing is justified by its ability to simulate synaptic plasticity through memristive switching, enabling local information storage and updating in a manner analogous to the functioning of synaptic weights.

Moreover, Nb:STO supports in-memory computing and helps overcome the von Neumann bottleneck, as it can both store data in different resistance states and perform computation (such as matrix-vector multiplication) within the same physical location. However, a detailed understanding of the physical phenomena involved in resistance state changes in this type of memristor remains crucial for drawing conclusions about its properties and potential applications. This remains the most significant challenge in memristor research.

### 1.3 Nb-doped SrTiO<sub>3</sub>

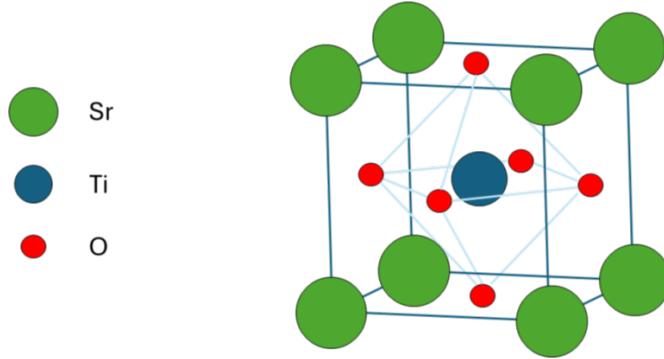

Oxide perovskites are materials that exhibit a general crystalline structure consistent with the chemical formula  $ABO_3$ , where A represents an alkali or alkaline earth metal, and B refers to a transition metal [3]. Regarding the spatial arrangement of these elements within the simple cubic lattice of perovskites, the B-site cation is located at the center of the cube (0, 0, 0), while the A-site cations are positioned at each of the cube's corners (1/2, 1/2, 1/2). Oxygen atoms occupy the centers of the cube faces (1/2, 1/2, 0).

The various particles that make up the general structure of oxide perovskites each play a specific role that influences the overall properties of the bulk material [37]. The A-site element acts as a large-radius cation, donating electrons and contributing to the thermodynamic stability of the structure. The B-site cations, which have smaller ionic radii, are responsible for regulating electrochemical reactions. However, the critical magnetic and electrical conductivity properties of these materials originate from the presence of oxygen within the lattice structure, as it forms the bonds between B-site atoms of adjacent lattices. This is because the modulation of the band structure in oxide perovskites largely depends on the orbital hybridization state present in the B–O–B bonds.

The material SrTiO<sub>3</sub> (STO) exhibits an almost ideal stoichiometry at room temperature, with a face-centered

**Figure 1.3.1:** Three dimensional cubic lattice of  $\text{SrTiO}_3$

simple cubic oxide perovskite structure. The lattice constant of bulk STO is  $3.928 \text{ \AA}$ , its indirect band gap is  $3.27 \text{ eV}$ , and its electron affinity is  $3.9 \text{ eV}$  [29]. Additionally, its high dielectric constant defines its insulating behavior under normal environmental conditions, reflecting a polar nature and low electrical conductivity in the presence of an electric field.

However, recent studies have shown that the dielectric constant of STO ( $\varepsilon_r$ ) is highly dependent on variations in temperature and electric field strength [31]. This is due to phase transitions to lower symmetry configurations, which promote oxygen non-stoichiometry and alter the electrical properties of STO. The relationship between these quantities is described by the Barrett formula [15]:

$$\varepsilon_r(T, E) = \frac{b(T)\varepsilon_0}{\sqrt{a(T + E^2)}}, \quad (1.3.1)$$

where  $\varepsilon_0$  is the vacuum permittivity, and  $b(T) = (1.3710^7 + 4.2910^7)(\frac{T}{100})$  and  $a(T) = a(T) = b(T)/\varepsilon_r(T, 0) \frac{b(T)}{\varepsilon_r(T, 0)}$ . The dielectric permittivity of the material under zero electrical field is given by:

$$\varepsilon_r(T, 0) = \frac{1635\varepsilon_0}{\coth(\frac{44.1}{T}) - 0.937}. \quad (1.3.2)$$

The formula predicts a decrease in the dielectric constant of  $\text{SrTiO}_3$  with increasing temperature. It aligns well with experimental results under moderate electric field conditions, where the dielectric permittivity saturates due to quantum fluctuations. However, under high electric field conditions, experimental measurements deviate from the relationship described by the Barrett formula [24].

All these properties, combined with its high melting point, low dielectric loss, low leakage current, and high Seebeck coefficient, have generated significant interest in this material [36].  $\text{SrTiO}_3$  is regarded as a universal substrate for epitaxially growing other oxides, as well as an active component in oxide heterostructures, demonstrating strong potential for applications in data storage and neuromorphic computing.

For this research, the oxide-based memristor is fabricated on a thin film of Nb-doped  $\text{SrTiO}_3$  substrate, which alters the original stoichiometry responsible for the insulating properties of pristine STO. Niobium atoms partially substitute the titanium cations located at the B-sites of the crystal lattice, resulting in a

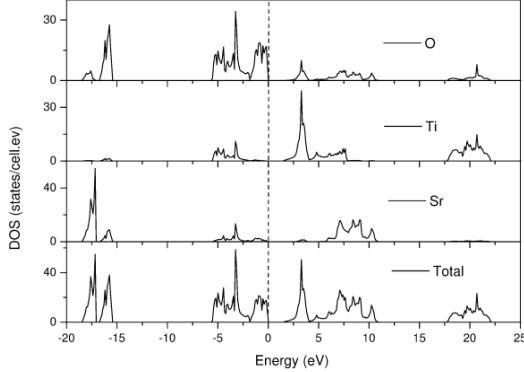

(a) DOS of  $\text{SrTiO}_3$

(b) DOS of  $\text{Nb:SrTiO}_3$

**Figure 1.3.2:** Comparison of the Density of States of  $\text{SrTiO}_3$  and  $\text{Nb:SrTiO}_3$  for different doping concentrations [36].

composition of  $\text{SrTi}_{1-x}\text{Nb}_x\text{O}_3$ . While  $\text{Ti}^{4+}$  cations contribute four electrons to the overall structure of the strontium-based perovskite,  $\text{Nb}^{5+}$  cations act as n-type doping agents, donating five electrons. This creates an artificial electronic imbalance, which is compensated by introducing one free electron into the conduction band for each  $\text{Nb}^{5+}$  ion added. With a sufficiently high dopant concentration, STO can exhibit behavior characteristic of an n-type semiconductor, where the Fermi level is shifted toward the conduction band.

Previous studies conducted by the Spintronics of Functional Materials research group have demonstrated some of the properties of Nb:STO that justify the growing interest in this material for computational applications [15], [11], [10], [30]. Unlike conventional semiconductors, the carrier concentration in Nb:STO remains nearly constant despite variations in temperature. The high dielectric permittivity of STO, even at very low temperatures, explains niobium's ability to remain ionized under these conditions, since the binding energy is inversely proportional to the square of the permittivity. This relationship is expressed by the following formula:

$$E_D = -13.6eV \left( \frac{m_e^*}{m_e} \right) \left( \frac{1}{\epsilon_r^2} \right), \quad (1.3.3)$$

where  $m_e^*$  represents the effective mass of the electrons and  $m_e$  denotes the mass of a free electron. The binding energy is minimal under very low temperature conditions, which means that Nb behaves as a shallow donor, requiring little energy for its ionization in such conditions. This favors the absence of freeze-out and results in a carrier concentration that is independent of temperature [4].

In contrast, the mobility of carriers in Nb:STO increases significantly as the temperature decreases. Furthermore, if the Nb doping concentration is sufficiently high, the oxide heterostructure can become a degenerate semiconductor capable of exhibiting metallic behavior. When these two parameters are properly exploited, it is possible to induce a superconducting transition, which highlights the remarkable versatility of Nb:STO and the wide range of functionalities it can offer in various applications [32].

## 1.4 Scope and Structure

The purpose of this research is to investigate the properties of Co/Nb:STO and evaluate its potential as a key material in the development of neuromorphic computing devices. In particular, the study explores the effects of device miniaturization down to 300 nm, on its I/V characterization, as well as device-to-device variability, endurance, retention characteristics, and transient behavior. Additionally, a theoretical model is proposed to account for the physical mechanisms underlying the resistance state changes observed in Co/Nb:STO.

**Figure 1.3.3:** Temperature dependence of carrier concentration and mobility for 0.01 and 0.1 wt % Nb doped  $\text{SrTiO}_3$  in the temperature range from 100 K to 300 K [30].

To this end, the theoretical principles related to the memristive behavior of the material are presented in Chapter 2. The fabrication process of Co/Nb:STO, carried out at the Nanolab Groningen facilities, is described in detail in Chapter 3, along with the methods employed for the electronic characterization of these devices. Chapter 4 presents the experimental results and their subsequent discussion. Finally, Chapter 5 summarizes the conclusions drawn from the analysis of the results.

# Chapter 2 Theoretical Background

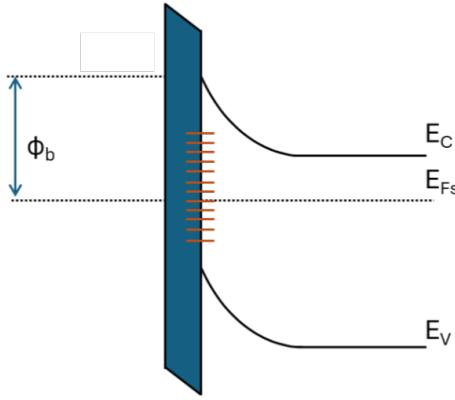

Once the metal/n-type semiconductor contacts are formed in the Co/Nb:STO memristor, the characteristic potential barrier of such heterojunctions is established. The higher work function of cobalt (5 eV) [12] compared to that of the semiconductor (4.2 eV) [25] results in the formation of a Schottky contact, which accounts for the electrical characteristics of the device. This section discusses the formation process of the Schottky barrier, its variations under voltage bias, the mechanisms involved in carrier transport through the barrier, and the resistive switching theory underlying the memristive behavior of Co/Nb:STO [34], [19].

## 2.1 Schottky Barrier Formation

Before the materials come into contact, the energy band profiles of each are configured as shown in the diagram in Figure 2.1.1a. The Fermi energy corresponds to the highest energy level at which the probability of finding an electron is fifty percent at absolute zero temperature (0 K). All energy levels below this point are fully occupied by carriers, while those above remain empty. The work function values are specific to each material and determine the position of their respective Fermi levels. In this case, the work function of Co is greater than that of Nb:STO, meaning that the Fermi level of the metal initially lies lower than that of the semiconductor, fulfilling a fundamental condition for the formation of a Schottky barrier in such contacts. Furthermore, the position of the Fermi level in the semiconductor relative to the conduction and valence bands depends on the carrier concentration. Since we are dealing with an n-type semiconductor, the concentration of free conduction electrons in the conduction band is higher, which explains the Fermi level being located near the conduction band.

Once contact between both materials is established, the Fermi levels tend to align in order to reach thermodynamic equilibrium, which alters the overall band profile, as shown in the Figure 2.1.1b. This energy level shift is caused by the migration of majority carriers across the junction. Electrons from the semiconductor, having a higher electrochemical potential, naturally flow toward lower potential states in the metal. However, since the metal side has an extremely high electron density, its Fermi level remains essentially unchanged when a small number of electrons are added or removed. Therefore, the equilibrium is reached primarily through the adjustment of the semiconductor's Fermi level.

As electrons leave the semiconductor, they leave behind positively charged fixed dopants, which generate an electric field at the junction interface. This newly formed field opposes the initial electron flow, creating a depletion region near the semiconductor interface that reduces the mobility of the majority carriers. As a result, the conduction and valence bands of the semiconductor bend upward near the interface, and a potential barrier is formed that limits electron flow toward the metal. This potential difference is known as the Schottky barrier.

The height of the Schottky barrier at equilibrium ( $e\phi_b$ ), relative to the equilibrium Fermi level, depends on the metal's work function and the electron affinity of the semiconductor, which defines the energy required to release an electron from the conduction band. This characterization of the Schottky barrier opposes the movement of majority carriers from the semiconductor and is described by the Schottky-Mott relation:

$$e\phi_b = e\phi_m - e\chi_s, \quad (2.1.1)$$

**Figure 2.1.1:** Energy band diagram of a metal and an n-type semiconductor junction before and after contact.

where  $\phi_m$  is the workfunction of the metal,  $\chi_s$  is the electron affinity of the semiconductor, and  $e$  the elementary charge.

On the other hand, the built-in potential ( $V_{bi}$ ) resulting from the shift in the Fermi levels is determined by the difference between the work functions of the two materials and is associated with the change in the semiconductor's Fermi level from its initial position during alignment. This potential represents the effective barrier that electrons originating from the semiconductor experience as they traverse the interface toward the metal side.

$$eV_{bi} = e\phi_m - e\phi_s, \quad (2.1.2)$$

where  $\phi_s$  is the workfunction of the semiconductor.

In such cases, the potential barrier associated with the built-in potential is generally lower than the Schottky barrier. This difference, along with the unequal electron concentrations on each side of the metal/semiconductor junction, enables the system to reach thermodynamic equilibrium. The depletion region also plays a crucial role in this balance; its width depends on the dielectric permittivity of the semiconductor, the donor concentration, and the built-in voltage.

$$W = \left( \frac{2\epsilon(V_{bi} - V)}{eN_d} \right)^{1/2}, \quad (2.1.3)$$

where  $N_d$  is the donor concentration.

## 2.2 Schottky Barrier Under Bias

Both the width of the depletion region and the value of the built-in effective potential barrier, as described in equations 2.1.2 and 2.1.3, can be modified by applying an external voltage. Depending on the polarity of this voltage, different structural changes can be induced in the energy band profile of the heterojunction, which may enhance the flow of current across the interface in a specific direction. In this context, two distinct cases can be identified: forward bias and reverse bias.

**Figure 2.2.1:** Energy band diagram of a Schottky contact under forward and reverse bias.

When a negative bias  $V$  is applied to the semiconductor side of a Schottky junction and a positive bias to the metal side, the applied voltage corresponds to the forward bias regime. In this case, all the energy levels of the semiconductor, including its Fermi level, are shifted upward, and become higher with respect to the Fermi level of the metal. According to equation 2.1.3, the width of the depletion region is reduced compared to its configuration at equilibrium. Additionally, since the work function of the semiconductor also decreases, the effective potential barrier ( $\phi_b^{\text{eff}}$ ) associated with the built-in potential is reduced relative to its height in the equilibrium state, and takes the following form:

$$\phi_b^{\text{eff}} = \phi_b - V. \quad (2.2.1)$$

All of this results in an increase in the forward current from the semiconductor to the metal, as the depletion region and the effective potential barrier offer less resistance.

On the other hand, the reverse regime is achieved by applying a negative bias to the metal side and a positive bias to the semiconductor side. In this way, the Fermi Level of the semiconductor and its energy bands become lower relative to the Fermi Level of the metal. Under these conditions, equation 2.1.3 predicts an increase in the depletion region of the Schottky contact, pushing the conduction band electrons further away from the interface. Due to the downward shift of the Fermi Level, the effective potential barrier increases significantly, further hindering current flow in the forward direction. The height of the new potential barrier is:

$$\phi_b^{\text{eff}} = \phi_b + V, \quad (2.2.2)$$

where  $V$  now gets negative values and the effective potential barrier is increased.

However, as the Fermi level of the semiconductor decreases, the Schottky barrier becomes steeper and thinner. When the energy of the conduction band becomes sufficiently lower compared to the Fermi energy of the metal, the probability of electrons tunneling through the potential barrier increases, thereby enhancing the current in the reverse direction.

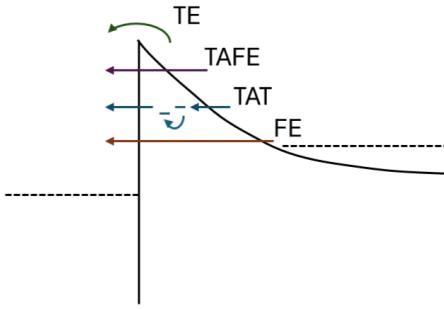

**Figure 2.2.2:** Diagram of the carrier transport mechanisms

## 2.3 Carrier Transport

When a potential difference is applied across the Schottky contact, the structural changes in the band profile discussed in the previous section explain the rectifying behavior of this type of heterojunctions, allowing current to flow in a specific direction. Depending on the polarity of the voltage bias, current can flow either from the semiconductor to the metal in a forward bias scheme, or from the metal to the semiconductor in a reverse bias regime.

The electric current arises from the movement of carriers overcoming the Schottky barrier across the interface, which is governed by the mechanisms of Thermionic Emission and Tunneling as shown in Figure 2.2.2.

### 2.3.1 Thermionic Emission

Thermionic emission refers to the movement of charge carriers over the Schottky barrier due to their own thermal energy. Only those electrons with sufficient energy to overcome the potential barrier are able to move from one side of the junction to the other through this mechanism. Assuming that the Schottky barrier height is significantly higher than the thermal energy under ambient conditions ( $k_B T$ ), and that thermal equilibrium at the interface remains unchanged despite the net current flow, the current density in the forward direction from the semiconductor to the metal is given by the Thermionic Emission Equation:

$$J_{s \rightarrow m} = A^* T^2 \exp\left(-\frac{e\phi_b}{kT}\right) \exp\left(\frac{eV}{kT}\right), \quad (2.3.1)$$

where  $J$  is the current density,  $k_B$  is the Boltzmann constant, and  $T$  the temperature.  $A^*$  is defined as the Richardson-Dushman constant and represents a material-dependent parameter related to the transmission rate due to thermionic emission. The expression for this constant is:

$$A^* = \frac{4\pi e m_e^* k^2}{h^3}, \quad (2.3.2)$$

where,  $m_e^*$  corresponds to the effective mass of the electrons, and  $h$  is the Planck constant. In the case of Nb:STO, the value of the Richardson constant is  $156 \text{ Acm}^{-2} \text{K}^{-2}$ .

In the expression for the current density in the forward direction, the applied voltage is taken into account, as the effective potential barrier for carriers on the semiconductor side can be modified under bias. However,

---

the potential barrier opposing the flow of charge in the reverse direction from the metal to the semiconductor is voltage-independent, since the Fermi level of the metal remains fixed. Therefore, the current density in the reverse direction can be obtained from Equation 2.3.1 by setting  $V = 0$ , resulting in:

$$J_{m \rightarrow s} = -A^* T^2 \exp\left(-\frac{e\phi_b}{kT}\right). \quad (2.3.3)$$

By summing the contributions in both directions, the net current density due to thermionic emission is given by:

$$J_{TE} = A^* T^2 \exp\left(-\frac{e\phi_b}{kT}\right) \left[ \exp\left(\frac{eV}{nkT}\right) - 1 \right], \quad (2.3.4)$$

where an ideality factor  $n$  is included. This factor equals one in the case of ideal thermionic emission. However, if defects are present in the heterojunction or if other mechanisms are involved in carrier transport across the interface,  $n$  will take values greater than 1. These additional transport mechanisms are typically associated with tunneling processes.

### 2.3.2 Tunneling

Tunneling encompasses all carrier transport mechanisms in which electrons are able to pass through an energy potential barrier via this quantum phenomenon. These processes allow electrons to cross from one side of the interface to the other, even when they lack the energy required to overcome the potential barrier in a classical manner as is the case in thermionic emission. When electrons with minimal energies near the Fermi level tunnel through the barrier, the mechanism is referred to as Field Emission. However, the tunneling phenomenon can also be facilitated by the thermal excitation of these electrons to higher energy levels, where the effective potential barrier becomes narrower and the likelihood of crossing via Thermally Assisted Field Emission increases. Both Field Emission mechanisms are strongly quantum in nature and are highly sensitive to changes in doping concentration and temperature, which significantly influence the potential barrier profile.

A comprehensive description of the current density across the Schottky barrier, which includes tunneling contributions from field emission and thermally assisted field emission, is provided by the Padovani and Stratton model, whose expression takes the form:

$$J_T = \frac{q^3 E^2}{8\pi h \phi_b} \exp\left(-\frac{8\pi\sqrt{2m^*}\phi_b^{3/2}}{3qhE}\right), \quad (2.3.5)$$

where,  $h$  refers to the Planck constant,  $E$  is the electric field strength, and  $q$  is the charge. This model assumes specific conditions of low temperature and high doping, highlighting the complexity of developing a mathematical expression that accurately describes the tunneling effect across the barrier and remains broadly applicable.

Equation 2.3.5 incorporates both tunneling mechanisms discussed; however, the current density associated with each can be defined separately. In the case of field emission transport, the expression is given by:

$$J_{FE} = \frac{A^{**} T \pi}{c_1 k \sin(\pi c_1 kT)} \exp\left[\frac{e(\phi_b - V)}{E_{00}}\right] \quad \text{with} \quad c_1 \equiv \frac{1}{2E_{00}} \log\left[\frac{4(\phi_b - V)}{-\xi}\right]. \quad (2.3.6)$$

The expression for the fraction of current density associated with thermally assisted field emission is:

**Figure 2.3.1:** Interfacial layer and trapping states in non-ideal Schottky contact.

$$J_{TAFE} = \frac{A^{**}T\sqrt{\pi E_{00}e(\phi_b - \xi - V)}}{k \cosh(E_{00}/kT)} \exp\left[\frac{-e\xi}{kT} - \frac{e(\phi_b - \xi)}{E_0}\right] \exp\left(\frac{eV}{E_0}\right), \quad (2.3.7)$$

where  $E_0 \equiv E_{00} \coth\left(\frac{E_{00}}{kT}\right)$ .

In order to determine which of the discussed carrier transport mechanisms is dominant under specific temperature and doping conditions, the characteristic energy parameter  $E_{00}$  is defined. Its expression is:

$$E_{00} = \frac{e\hbar}{2} \sqrt{\frac{N_d}{m_e^* \epsilon_r}} \quad (2.3.8)$$

where  $\hbar$  is the reduced Planck constant. By comparing this energy parameter with the average thermal energy available to electrons at a given temperature, expressed as  $k_B T$ , it is possible to determine which of the three transport mechanisms contributes most significantly to carrier transport. If  $E_{00}$  is much smaller than  $k_B T$  ( $E_{00} < k_B T$ ), simple field emission is the dominant process. Conversely, if  $E_{00}$  is much greater than  $k_B T$  ( $E_{00} > k_B T$ ), thermally assisted field emission becomes the prevailing mechanism. If  $E_{00}$  is approximately equal to  $k_B T$  ( $E_{00} \simeq k_B T$ ), then thermionic emission is the primary transport mechanism across the barrier, taking precedence over tunneling.

However, this parameter only accounts for direct band-to-band transport mechanisms. In the Schottky junction formed by oxide perovskites, such as the interface between Co and Nb:STO, another highly relevant transport process involves energy states present at the interface. This phenomenon is known as Trap Assisted Tunneling, and it plays a crucial role in the switching and distinction between the two characteristic resistance states in memristive materials.

### 2.3.3 Resistive Switching by Trap Assisted Tunneling

In the derivations obtained in previous sections, the formation of an ideal Schottky contact was considered, where materials come into contact in a perfect vacuum and are free of defects and impurities. Although this approach allows for the correct prediction of variations in the Schottky barrier profile and the approximate current behavior, numerous non-ideal agents modify these derivations. These irregularities are key to understanding the operation of Co/Nb:STO contacts.

During the fabrication process of Co/Nb:STO memristors, it's crucial to consider numerous impurities related to the surface energy of the semiconductor material and its characteristics. First, oxide perovskites

---

very commonly show a high level of oxidation on their surface. This can generate a very thin interfacial layer between the metal-semiconductor junction with insulating properties. This new feature in the non-ideal Schottky contact modifies its energy band profile as shown in Figure 2.3.1.

The presence of this insulating layer causes an additional voltage drop of the built-in potential across it. As a result, there's a deviation from the ideal Schottky-Mott limit, where the Schottky barrier is determined solely by the metal's work function and remains constant. In this case, the effective Schottky barrier that charges experience becomes bias-dependent and can be altered.

Additionally, Nb:STO has numerous oxygen dangling bonds on its surface. The presence of these incomplete surface terminations during the fabrication of the heterojunctions creates a series of interface states capable of trapping charges moving from side to side. This transport mechanism, where carriers can tunnel between both sides of the Schottky contact through these trapping states, is called Trap-Assisted Tunneling. Although the density of interface trap states depends on the cleaning, preparation, and fabrication processes, their formation is mainly due to the stoichiometric properties of the Nb:STO material, representing a structural consequence in the development of these memristive devices.

The occupation of trapping states at the interface by electrons is governed by the Fermi-Dirac distribution for fermions. Thus, since all energy levels located below the Fermi Level are fully occupied, the same rule applies to the trapping states. Consequently, in the Co/Nb:STO Schottky junction, the trapping and detrapping of carriers at the interface states largely depend on the Fermi Level's position, which can be modulated by applying a voltage bias.

When a forward bias is established from equilibrium, the semiconductor's quasi-Fermi level moves closer to the conduction band, increasing the probability that electrons moving from the semiconductor to the metal will be trapped at the interface. The trapped carriers cannot contribute to the generated current, leading to a high resistance state (HRS). Conversely, when the voltage polarity is switched and the forward bias is reduced to equilibrium, the Fermi level returns to its initial position. During this process, the charges previously trapped at the interface begin to release and reach the metal side, enhancing the resulting current and switching to a low resistance state (LRS). If the voltage continues to decrease and a reverse bias is applied, the semiconductor's Fermi level will continue to drop, approaching the valence band. The number of available interface states under these conditions remains very high, facilitating the transport of carriers from the metal to the semiconductor via trap-assisted tunneling. This, combined with the reduced width of the Schottky barrier, results in low resistance, and the LRS is maintained. Finally, if the voltage polarity is reversed again, the Fermi level will start to rise from the valence band and return to its equilibrium state, favoring the occupation of the states present at the interface. This reduces the number of available states for trap-assisted tunneling, thereby increasing the resistance to current flow in the reverse direction. The HRS is thus re-established.

This voltage-controlled modulation of the trapping states' occupation provides the foundation for the memristive behavior of Co/Nb:STO, in which two well-defined resistance states can be interchanged through bipolar resistive switching mechanisms. The voltage values at which the High Resistance State (HRS) is switched to a Low Resistance State (LRS) are referred to as SET voltages. Conversely, the voltage values at which the LRS is switched back to the HRS are known as RESET voltages. Although this model makes it possible to explain the electrical properties of the device under test, it remains a basic conceptualization of the complex physical processes involved. Yet, it remains useful for the development of this research work.

# Chapter 3 Methodology

The memristive properties of Co/Nb:STO are largely attributed to the crystal structure of the materials and to the inherent imperfections present on their surfaces. Therefore, it is crucial to design a precise and rigorous fabrication process that enables the creation of functional devices capable of exhibiting the desired response during their electrical characterization. This section outlines the steps carried out in the cleanroom for the fabrication of the Co/Nb:STO contacts, as well as the methods employed during their testing using the Keysight B1500A Device Analyzer [1].

## 3.1 Device Fabrication

### 3.1.1 Sample Preparation

#### **TiO<sub>2</sub> Single Terminated Surface**

The substrate of the fabricated device consists of Nb-doped SrTiO<sub>3</sub> with a donor concentration of 0.01 wt% Nb. Depending on the crystal structure of oxide perovskites, it is possible to observe the surface of SrTiO<sub>3</sub> entirely covered by terminations of a single type, corresponding to a thin oxidation layer formed either by SrO or TiO<sub>2</sub>. However, the crystal structure of the material provided by the supplier exhibits a mixed-terminated layer, composed of a combination of both types of terminations mentioned above. Although this structure provides greater thermodynamic stability, a single termination on the surface of the perovskite enables the construction of (111)-oriented SrTiO<sub>3</sub> with more functional physical properties and more homogeneous interfaces [28]. Since a single TiO<sub>2</sub>-terminated layer features greater energetic stability, the surface structure of Nb:STO was modified through a controlled selective chemical wet etching process, taking advantage of the different etching rates of the Sr and Ti terminations [20].

First, the substrate is cleaned using successive ultrasonic baths filled with acetone, ethanol, and isopropanol. Cleaning occurs when the sound waves agitate the solvent-based liquid, causing cavitation or bubbling of the impurities and contaminants present on the surface. The resulting molecular explosions generate enough force to dislodge dirt and other contaminants from the surface of the immersed substrate. Once the solvent baths are completed, the substrate is again submerged and ultrasonicated in deionized (DI) water for 30 minutes to complete the cleaning process. In this way, the SrO terminations are hydroxylated, leading to the formation of Sr(OH)<sub>2</sub>.

In order to remove the Sr(OH)<sub>2</sub> and obtain a TiO<sub>2</sub>-terminated surface, the substrate is etched with buffered HF acid for 30 seconds.

Once the process is completed, the sample is ultrasonicated in DI water one final time, cleaned with ethanol, and dried with *N*<sub>2</sub>.

#### **Thermal Annealing**

Thermal annealing consists of removing any remaining cleaning agents previously used by controlling the temperature and adjusting the oxygen pressure. Additionally, the crystalline lattice of Nb:STO is restruct-

**Figure 3.1.1:** Typical structure of the optical column of an Electron Beam Lithography machine.

tured due to the diffusion and rearrangement of particles at the surface, which leads to a reduction in surface energy. For this purpose, the substrate is annealed at 960°C under an O<sub>2</sub> flow of 300 cc per minute. The duration of the process depends on the thickness of the substrate.

As a result of the annealing process, the surface of the material exhibits reduced roughness and more pronounced height variations, corresponding to well-defined stepped terraces.

### Electron Beam Lithography

The fabrication of the Schottky contacts is based on the deposition of Co onto the Nb:STO substrate. To achieve this, the desired pattern is transferred using Electron Beam Lithography (EBL), a maskless fabrication technique used to write nanostructures by means of a focused beam of electrons (e-beam) directed at a resist-coated substrate. The resist material on top of the substrate is electron-sensitive, meaning its chemical composition and solubility can be altered through exposure to the electron beam. In this way, regions with different exposure levels can be selectively dissolved during the development process, as they become more or less soluble depending on the type of resist used and the intensity of the high-frequency e-beam. The electron beam can be focused to below 10 nm, making this technique not diffraction-limited and enabling fabrication with a high level of precision and accuracy [16].

The lithographic process is carried out using the Raith e-Line Plus system, which includes a column equipped with an electron gun capable of generating an electron beam with energies ranging from 20 eV to 30 keV ([16]). The system also incorporates various optical components such as lenses, aligners, and deflection coils, which control the position, alignment, and focusing of the e-beam. Additionally, a beam blanker is included to switch the e-beam on and off, enabling the transfer of the desired pattern onto the material without the need for masks.

The sample is placed on a mechanical stage, allowing for easy positioning under the e-beam. Figure 3.1.1 presents a general diagram of the column in an EBL system. All these components can be controlled computationally during the lithographic process, which must be conducted under high-vacuum conditions to prevent electron diffraction by air particles. The optimal pressure to achieve reliable results is approximately 510<sup>-7</sup> mbar.

The high precision and accuracy of the EBL technique can be attributed to the high energy of the e-beam. In this experiment, the emitted electrons are accelerated to an energy of 10 keV. Using the de Broglie wavelength formula,  $\lambda = \sqrt{(h/2mE)}$ , the electron beam corresponds to a wavelength of 7.0810<sup>-3</sup> nm, an

**Figure 3.1.2:** General setup of an electron beam evaporation machine.

extremely low value compared to other state-of-the-art lithographic techniques such as Extreme Ultraviolet Lithography (EUV) ??.

As a result, the smallest possible feature size is not diffraction-limited; instead, the minimum beam spot size and the specific experimental procedure become the most critical factors. Furthermore, the photoresist material introduces an additional variable, as its composition can influence the number of scattering events, potentially reducing the overall resolution.

### Electron Beam Evaporation

The deposition process of the material onto the sample is carried out via electron beam deposition, using the Temescal Thin Film Coater 2000 (TFC-2000) system. This physical vapor deposition technique enables the heating of materials with extremely high boiling points by means of a focused beam of high-energy electrons, properly directed using a magnetic field. The target material is placed in a water-cooled crucible inside a vacuum coating chamber. The substrate is positioned just above the source, allowing the evaporated particles to flow upward and adhere to its surface under high-temperature and low-pressure conditions.

The electron beam is rastered over a wider area of the target material rather than focusing on a single point, thereby avoiding localized overheating. To prevent undesired or accidental deposition on the sample, shutters are placed between the substrate and the source. These shutters function as gates that open only when the deposition rate, monitored by sensors integrated into the system, reaches a stable and constant value. The general layout of the components in the electron beam deposition system is shown in Figure 3.1.2. For optimal deposition without irregularities or defects, the process must be carried out under high vacuum conditions, typically around  $1 \times 10^{-6}$  mbar.

### 3.1.2 Experimental Procedure

Once the sample has been prepared, the fabrication of the Co/Nb:STO device consists of two lithographic processes using EBL, each followed by its respective development, deposition, and lift-off phases. Both steps are schematically illustrated in Figure 3.1.3.

The first EBL step (3.1.3a), involves transferring circular patterns of various sizes onto the substrate, in preparation for the subsequent deposition of insulating AlOx across the entire surface—except in those patterned circles, which are intended to form the metal–semiconductor contacts. These heterojunctions are created during the second EBL step, which includes the deposition of Co and Au exclusively within the circles left uncovered by the AlOx layer as a result of the previous step.

**Figure 3.1.3:** Steps of the fabrication process of Co/Nb:SrTiO<sub>3</sub> memristive contacts.

Before initiating the first lithographic process itself, the annealed and single-terminated Nb:STO substrate must be carefully cleaned, and the negative e-beam resist AZ nLOF 2020 must be spin-coated onto its surface. The coating technique is designed to ensure a uniform distribution of the resist material over the substrate by means of a constant rotational speed of 3000 rpm for 1 minute. Once the spin-coating step is complete, the substrate must be soft-baked at 110 °C to eliminate any residual solvent and enhance the adhesion between materials.

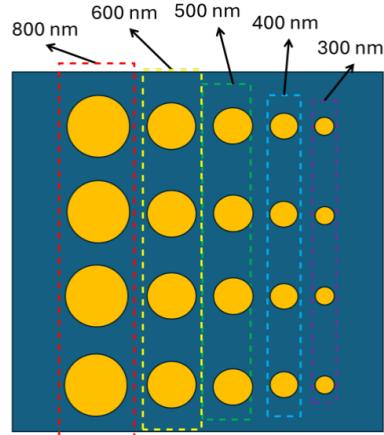

The desired initial pattern for the first lithographic step consists of a 44 × 5 array of circles left uncovered by the resist, arranged such that each column corresponds to a specific, predefined circle radius. The radii of the circles from the first to the fifth column are: 800 nm, 600 nm, 500 nm, 400 nm, and 300 nm, respectively. This pattern is illustrated in Figure 3.1.4b and is digitally defined in the Electron Beam Lithography (EBL) system.

Before starting the electron beam exposure, parameters such as focus, stigmation, and aperture positioning must be computationally optimized. Depending on the column to be written, variables such as aperture distance, electron beam current, and dose per unit area must be adjusted to suit each specific case. For the smaller circles, the dose per area must be increased in order to overcome relevant physical and material limitations at this scale, such as the proximity effect and resist contrast, among others [23] [13]. The exposure time for this first lithographic process was 30 minutes.

After exposure, the material is developed to make the designed pattern visible. This is achieved by immersing the sample in AZ MIF developer for 90 seconds, followed by rinsing in deionized (DI) water for 2 minutes. Since a negative e-beam resist was used, the areas that were exposed to the electron beam undergo a crosslinking reaction, becoming more insoluble and thus remaining adhered to the substrate after development. In contrast, the unexposed circular regions retain their original structure and dissolve more readily during the development process, thereby revealing the underlying substrate surface.

Next, a thin 50 nm insulating layer of AlO<sub>x</sub> is deposited onto the patterned sample using the electron beam evaporation machine, TFC-2000. The sample must be placed inside the system's load lock, and a pressure of approximately  $5 \times 10^{-6}$  mbar is established within the chamber. The deposition of AlO<sub>x</sub> is carried out at a rate of 1 Å/s.

Once the deposition is complete, the lift-off process of the resist material is carried out by immersing the

(a) Fabricated device

(b) Diagram of the fabricated device with Co/Nb:SrTiO<sub>3</sub> contacts

**Figure 3.1.4:** Disposition of the fabricated devices in the measuring chip.

sample in an NMP (1-methyl-2-pyrrolidone) solution preheated to 80°C for 15 minutes. Then, the sample is ultrasonicated at maximum power for 99 minutes to remove any remaining solvent or resist residues. In this way, the first lithographic step of the fabrication process is completed, resulting in an Nb:STO substrate fully covered by AlO<sub>x</sub> except for circular areas of varying diameters where the substrate surface remains exposed. Under this configuration, the circles are now electrically isolated from each other and from the rest of the substrate.

In the second step of the fabrication process, the EBL technique is employed in the same manner to construct the metal-semiconductor contacts of the final device within the spaces provided by the previously designed and isolated circular openings. For this purpose, the Nb:STO substrate with the deposited AlO<sub>x</sub> layer is spin-coated again, this time with a positive e-beam resist. The resist used is PMMA 950K 4%, which is spin-coated at 4000 rpm for 1 minute. The sample is then soft-baked at 180 °C for 90 seconds.

The exposure is once again carried out using the EBL system, although in this case the process lasts for 1 hour. Subsequently, the e-beam resist is developed by immersing the sample in an MIBK:IPA solution for 60 seconds, followed by immersion in deionized (DI) water for the same duration. Since the resist material is positive, the exposed areas undergo chain scission, making them more soluble in the developer solution compared to the unexposed regions.

Finally, the second step is completed with the sequential deposition of thin layers consisting of 20 nm of Co and 120 nm of Au, one on top of the other, respectively. The deposition is carried out using the TFC-2000 system, where Co is deposited at a rate of 1 Å/s, while the Au layer is deposited at a rate of 3 Å/s. In this step, the sample is immersed in cold acetone for several days to facilitate the lift-off process. Afterwards, gentle ultrasonication is applied to the substrate to remove any remaining metal flakes.

In this way, the fabrication process is completed, resulting in an array of circular Schottky contacts of varying sizes formed by Co/Nb:STO. These contacts are electrically isolated from one another due to the presence of the AlO<sub>x</sub> layer. The Au layer deposited on top of the contacts serves to prevent the oxidation of Co, as gold is

an inert metal with low chemical reactivity. Figure 3.1.4a shows an image of the fabricated device after being mounted onto a chip carrier using a conductive silver paste.

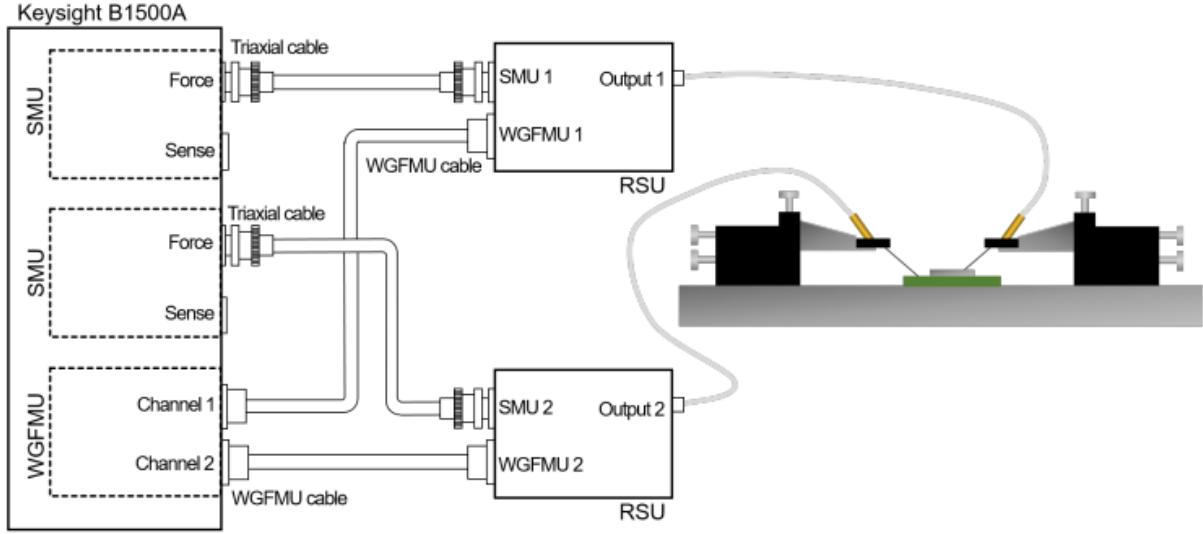

**Figure 3.1.5:** Experimental setup for the electrical characterization of samples using the B1500A Keysight Analyzer [10]

## 3.2 Electrical Characterization

Measurements of the electrical properties are fundamental for analyzing the behavior of the tested memristive device. The results obtained regarding the electrical characterization in this research were acquired using the Keysight B1500A Semiconductor Device Analyzer. The experimental setup for this process is shown in Figure 3.1.5 [10].

The Keysight B1500A Semiconductor Device Analyzer consists of a computer connected via various rear ports to up to 10 supported modules designed for specific measurements. The computer has integrated EasyEXPERT group+ software, which allows for selecting and configuring different measurement modes. The modes used for electrical characterization in this research are described in more detail in Appendix A, including: I/V Sweep, I/V-t Sample, I/V List Sample, and Pulsed wave generator measurements.

The most basic electrical measurements are performed using Source/Monitor Units (SMUs), which are connected to their respective modules. An SMU compactly integrates a current source, a power supply, an ammeter, and a voltmeter, allowing for rapid switching between these resources without manual hardware changes. These units are used in the most basic measurement modes, related to classic tests like I/V Sweep, I/V-t Sample, and I/V List Sample, where it's necessary to control a wide variety of parameters. The maximum measurement and sourcing power for voltage and current is 200 V and 1 A, respectively, with a resolution down to 0.5  $\mu$ V and 0.1 pA. Additionally, these units can produce voltage and current pulses in the 50  $\mu$ s range, as well as time-dependent measurements with a speed of 100  $\mu$ s.

The Waveform Generator/Fast Measuring Unit (WGFMU) module offers greater speed and precision in both supplying and measuring processes, enabling more advanced characterizations, including fast-pulsed and high-speed transient analysis. The waveform configuration supports pulses as short as 100 ns, and it's also possible to simultaneously measure current and voltage with a 5 ns sampling rate. This mode of operation is essential for analyzing the properties and applications of the devices under test in relation to their capabilities as memory units.

Two cables or probes are connected to each of these modules and are brought into contact with the device. One of the probes must be placed on the silver paste present on the chip carrier, while the other is carefully positioned directly on each of the Co/Nb:STO devices with the aid of a Dino-Lite digital camera with a 5-megapixel resolution.

# Chapter 4 Results and Discussion

In order to analyze the properties of the fabricated Co/Nb:STO devices, several I–V curves were obtained, reflecting the relationship between the voltage applied to the device and the resulting output current. These measurements were performed for all devices and analytically compared with one another. Additionally, the behavior of the devices under different voltage pulses was examined, allowing for discussion of the response speed, transient characteristics, and previously unexplored depression and potentiation properties, which offer promising potential for various applications.

## 4.1 Current-Voltage Characteristics

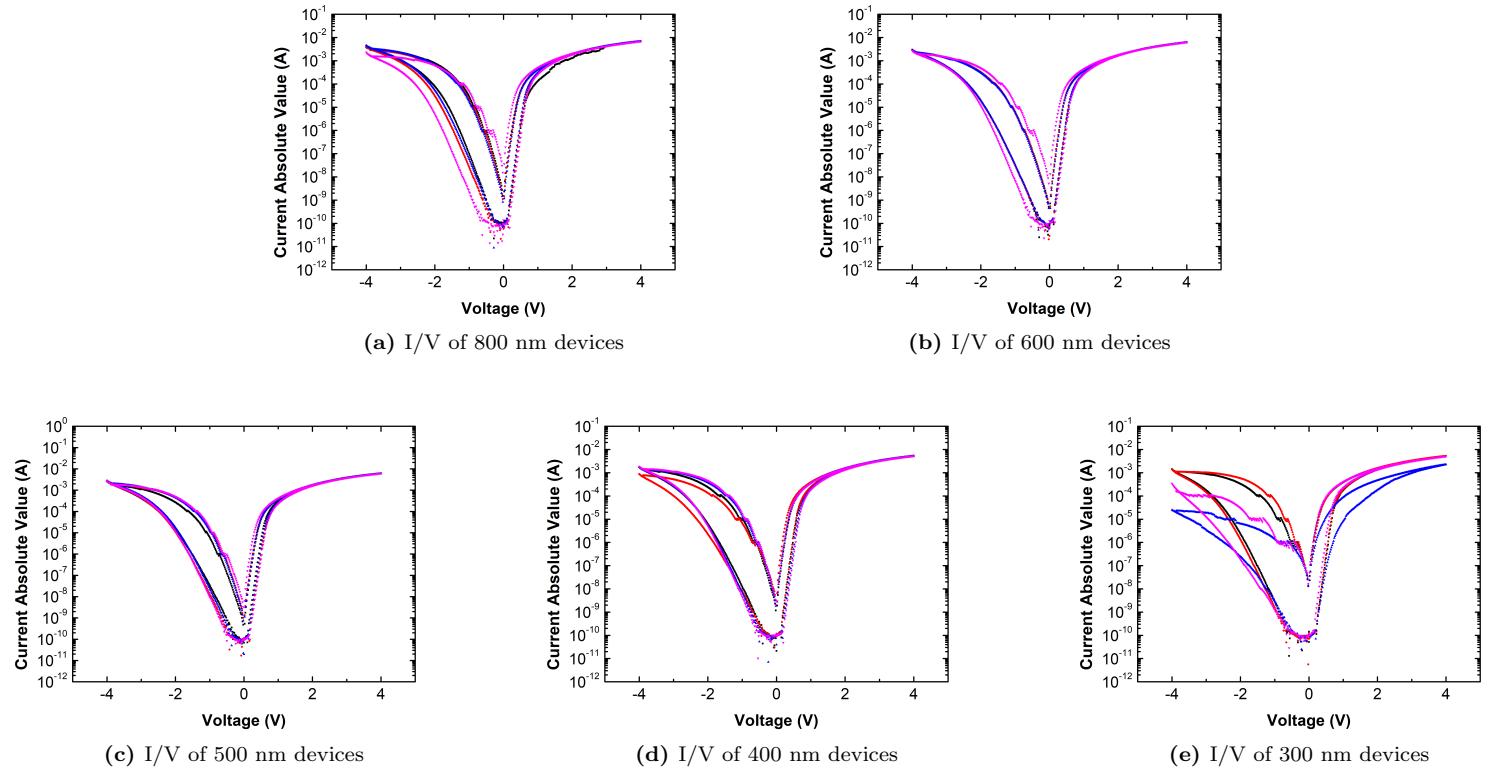

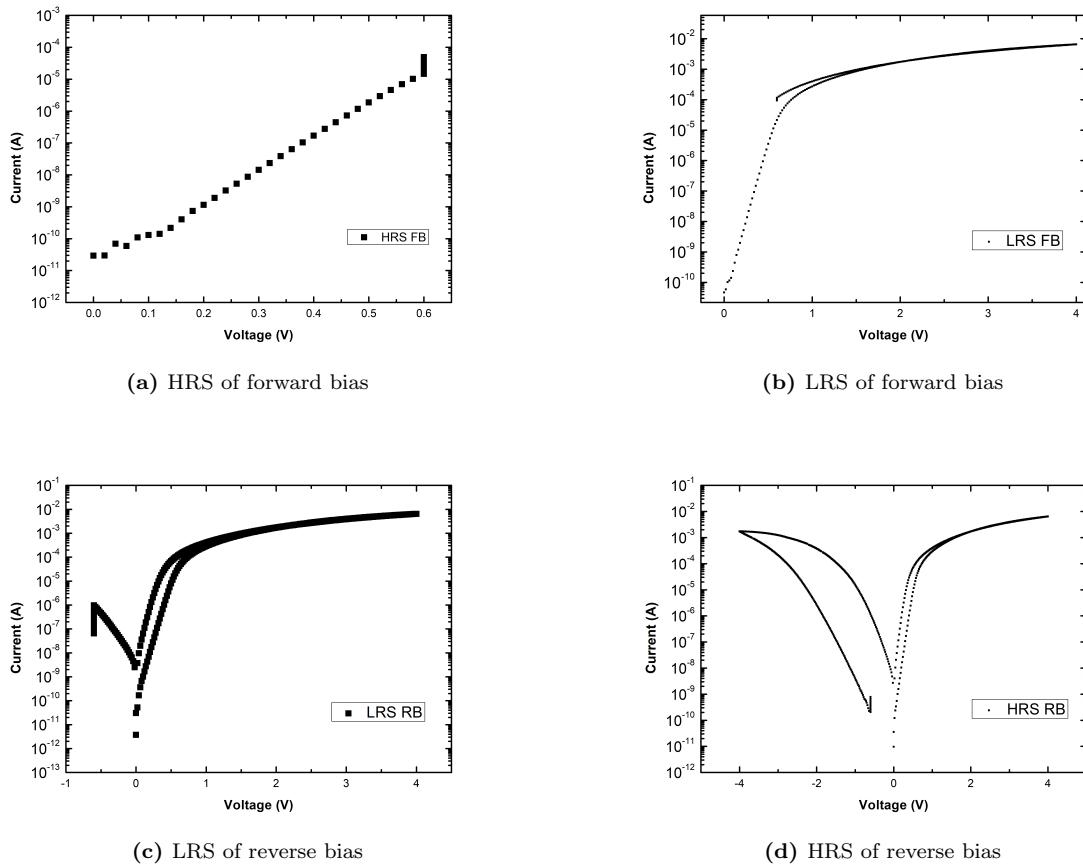

Multiple I–V measurements were performed on devices of identical size to compare the variability in their behavior and to identify any defective units with fabrication-related issues. Figure 4.1.1 displays several plots of the I–V characteristics from different devices of the same dimensions, where voltage sweeps were applied with an initial RESET voltage of -4 V and a SET voltage of 4 V. The terms SET and RESET voltages refer to the voltage values at which a polarity reversal of the applied potential induces the transition from the High Resistance State (HRS) to the Low Resistance State (LRS), and vice versa, respectively. This mechanism is known as bipolar resistive switching, which has been introduced already in Section 2.3.3.

Most devices exhibit a clear hysteretic behavior, characterized by two well-defined current branches at the same voltage value in both the forward and reverse bias regimes. The upper branch, associated with higher current levels, corresponds to the LRS, whereas the lower branch represents the HRS. This behavior confirms that the fabrication process was largely successful, effectively demonstrating the memristive properties of Co/Nb:STO. Only two of the smallest devices, shown in plot 4.1.1e deviate from this trend.

The gap between the current lines of each state is referred to as the dynamic range, which is more pronounced under reverse bias than under forward bias. However, both branches tend to saturate near the SET and RESET voltage values, where the two states converge and become indistinguishable. The fact that the dynamic range is narrower in forward bias compared to reverse bias can be explained by the different dominant carrier transport mechanisms in each regime, as well as the influence of trapping states on the overall current density. In forward bias, the primary transport mechanism is thermionic emission of carriers with sufficient energy to “jump” over the effective potential barrier, which is significantly reduced. Under these conditions, the likelihood of various tunneling processes is diminished, and their contribution to the current density toward the metal side is negligible. Consequently, trapping-assisted tunneling plays a secondary role under forward bias, reducing the differences between the LRS and HRS and limiting the memristive properties. In contrast, under reverse bias, carrier tunneling processes become highly relevant, as the potential barrier at the interface becomes thinner. As a result, trapping-assisted tunneling contributes more substantially to the overall current density toward the semiconductor, enhancing the differences between the LRS and HRS and increasing the dynamic range in the reverse bias regime.

Some LRS curves under reverse bias show a sudden step-like increase in current, corresponding to a change in its order of magnitude, as well as a crossing point and overshoot between the LRS and HRS branches within the same regime. These features have been attributed to limitations of the Keysight B1500A measurement system and have therefore been excluded from the analysis of Co/Nb:STO properties.

**Figure 4.1.1:** Current-voltage characteristics of several equal-sized devices.

Although minor differences are inevitable due to the inherent difficulty of fabricating perfectly identical contacts, the device-to-device variation is relatively low, as the I-V curves in each plot tend to overlap closely. This is a highly favorable feature, as it reflects the consistency, reliability, and predictability of these devices. These are some key characteristics for both practical applications and accurate modeling. Moreover, the variations among devices of the same size tend to decrease with miniaturization, suggesting an enhancement of the material's properties at smaller scales. Similar observations presented in the following sections support this claim, highlighting the high spatial and energy efficiency of Co/Nb:STO.

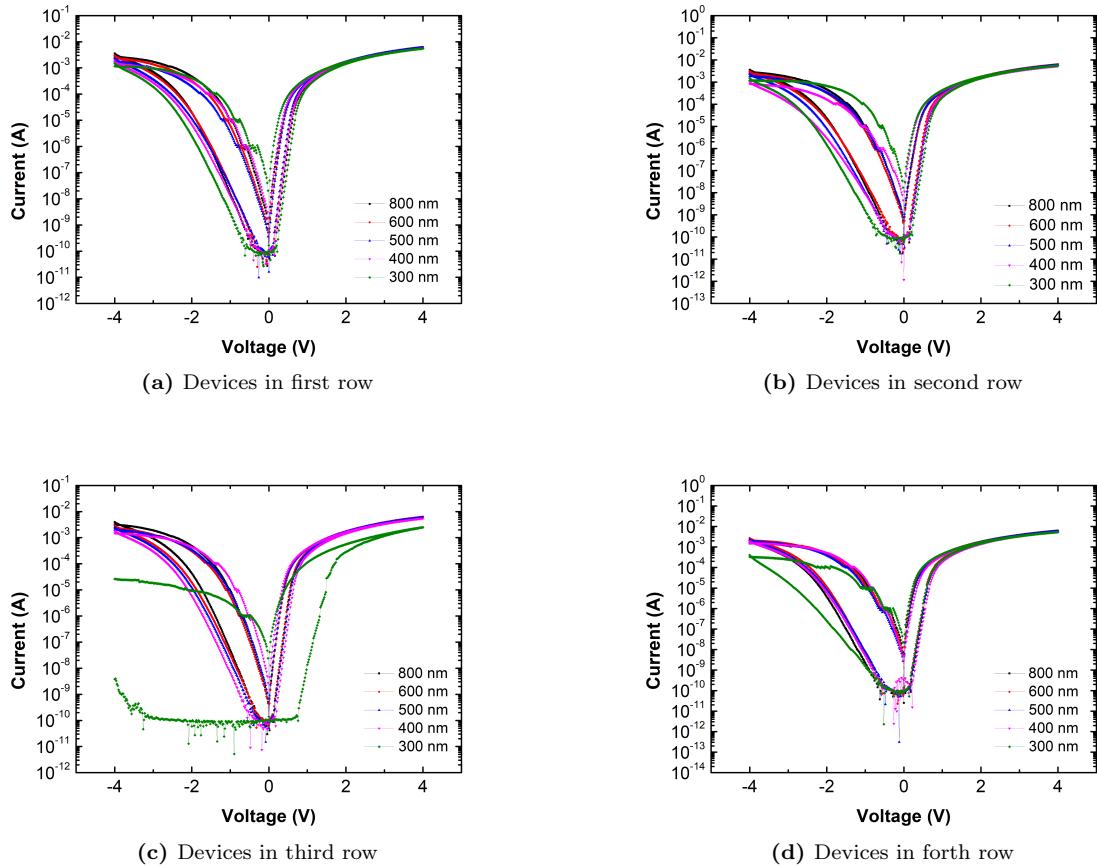

## 4.2 Device Scaling Effects

With the aim of analyzing the consequences of reducing device size, I-V curves were obtained using voltage sweeps with a RESET voltage of -4 V and a RESET voltage of 4 V. Figure 4.2.1 shows the size variation across a series of devices. The contact radius ranges from 800 nm down to 300 nm, the latter corresponding to the smallest Co/Nb:STO device ever fabricated at the Zernike Institute for Advanced Materials.

A clear increase in the dynamic range between the LRS and HRS was observed as device size decreased. This widening of the window is primarily attributed to the edge effect, which depends on the perimeter-area ratio [10]. This effect consists of the appearance of different properties on the surface of materials compared to the rest of the bulk, due to high surface energy. Therefore, the electrical characteristics of nanostructures near their edges can differ from the rest of the material. With respect to the electric field, the edge effect can result in a higher concentration of field strength on the surface, which is the basis for resistive switching behavior. In the case of smaller devices, the consequences of the edge effect become more evident, leading to a stronger differentiation between resistance states and thereby enhancing the memristive behavior and overall applicability of the material.

**Figure 4.2.1:** Current-voltage characteristics of devices with different sizes from 800 nm to 300 nm

Under reverse bias, the variation in the dynamic range is particularly pronounced, since the dominant carrier transport mechanism consists of several tunneling processes whose efficiency strongly depends on electric field strength. In contrast, under forward bias, the dynamic range exhibits more subtle variation, since trapping and detrapping of the interface states is not the main contribution to the current changes. In this regime, the main transport mechanism is thermionic emission of electrons over the Schottky potential barrier. This process is largely size-independent, and while tunneling contributes to the forward current density, its role is comparatively minor, making the influence of varying trapping state densities less significant.

### 4.3 RESET and SET Voltage Variations

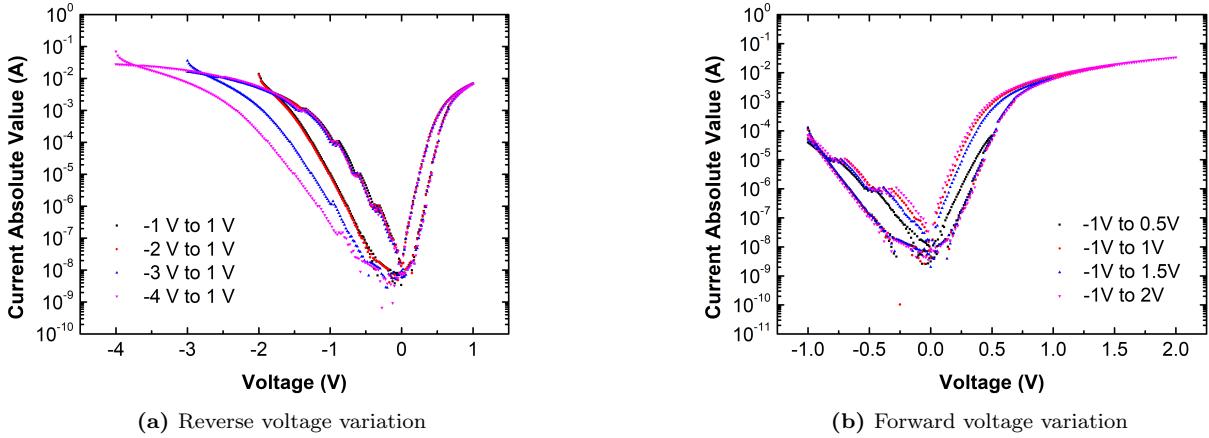

In Figure 4.3.1, the I-V characteristics of a single device are shown after performing several voltage sweeps in which the SET and RESET voltage values are varied.

In plot 4.3.1b, the SET voltage is fixed at 1 V, while the RESET voltage is varied from -1 V to -4 V. In this case, the hysteresis loop under forward bias remains unchanged. However, in the reverse bias regime, the loop expands to match the increasing voltage range, progressively extending further to the left. Although the LRS and HRS branches do not overlap, they do converge in all cases. The current lines associated with the LRS under reverse bias overlap perfectly across all voltage ranges, exhibiting the same slope variation and differing only in their extension along the voltage axis. In contrast, the HRS current lines in the reverse bias regime vary with the applied RESET voltage, showing no overlap while maintaining similar slopes. This behavior indicates a multilevel nature of the memristor under test, as intermediate resistance states between

**Figure 4.3.1:** Current-voltage characteristics of a device under voltage sweeps with different ranges.

the LRS and HRS can be accessed in the reverse bias regime. By modulating the RESET voltage range, this property can be enhanced, offering significant advantages for non-binary computational memory, particularly for multi-level cells (MLCs), which can respond with mid-step memory values and store more than a single bit of information [8].

On the other hand, plot 4.3.1a displays the I-V characteristics of the same device when the RESET voltage is fixed at -2 V, and the SET voltage is varied within a range from 0.5 V to 2 V. Under these conditions, the different loops in the reverse bias do not undergo significant changes, while the branches under forward bias extend further to the right. The current lines with lower values, associated with the HRS under forward bias, overlap with one another and become indistinguishable except for their extension along the voltage axis. However, the lines corresponding to the LRS in the forward bias show slightly different slopes and are marginally separated from each other, unlocking intermediate states too. Unlike the modulation of the RESET voltage range, the current gap between the intermediate lines within the memory window is smaller in this case, which would hinder non-binary memory applications, although it could still be feasible with proper device design.

These differences in the variation of states when altering the RESET versus the SET voltage are related to the overlap of the current lines at the limits of the voltage domain in each case. While the LRS and HRS lines under reverse bias modulation converge at different points, the lines corresponding to both states during forward bias modulation tend to overlap and converge at the same point. This phenomenon can be explained by the movement of the semiconductor's Fermi level and the occupation or release of interfacial trapping states, whose number is finite and limited. Once the maximum number of trapping states has been either occupied or released under forward and reverse bias respectively, the resulting current behavior becomes comparable to that observed under a constant voltage, with the Fermi level remaining fixed. This is because the number of available trapping states remains constant in both situations. Therefore, the current line behavior at the domain extremes in each plot resembles the transient current response of each state to a constant voltage pulse, as will be shown in Section 4.4. Ultimately, the overlap between the LRS and HRS lines under forward bias modulation arises from the nearly identical time-dependent resistance values of both states when the number of occupied trapping states reaches its maximum and becomes stable. In contrast, the LRS and HRS lines under reverse bias modulation do not overlap and diverge rapidly after converging, as the time-dependent resistance variations between these states are significantly different.

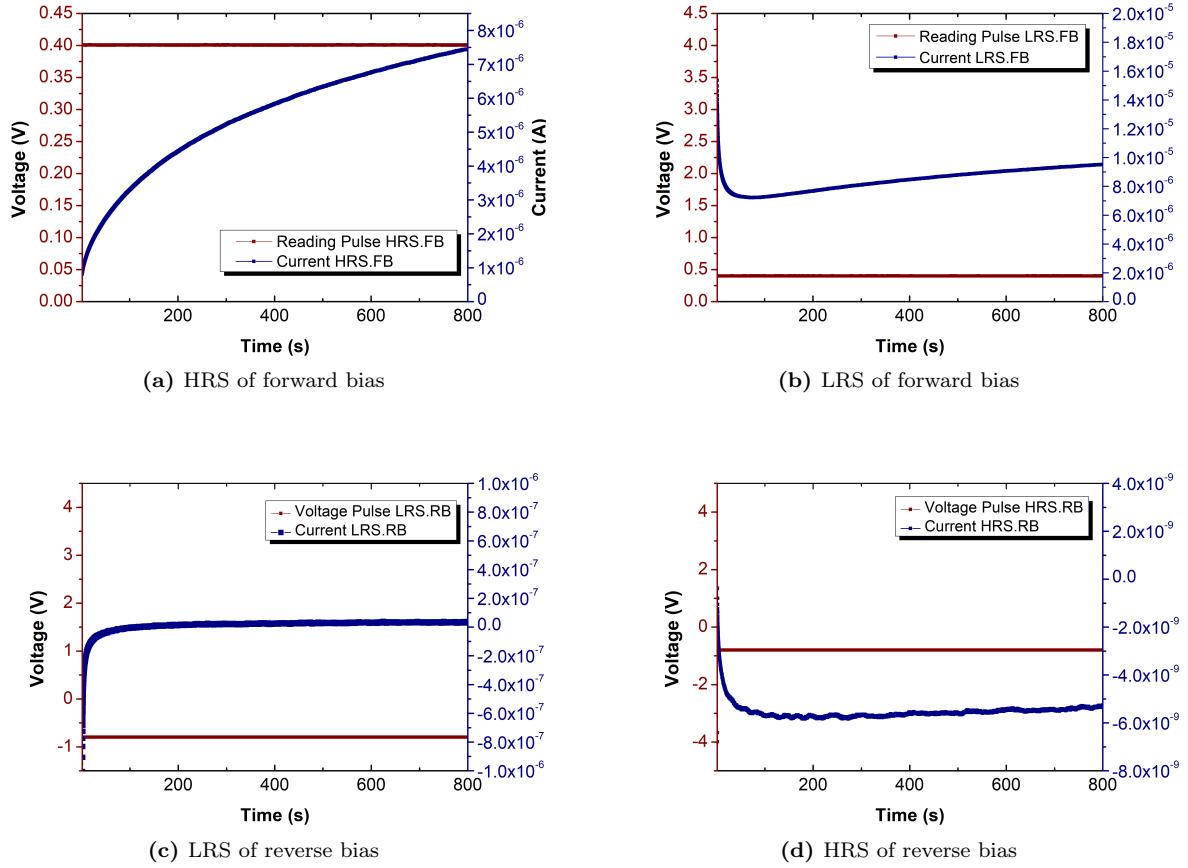

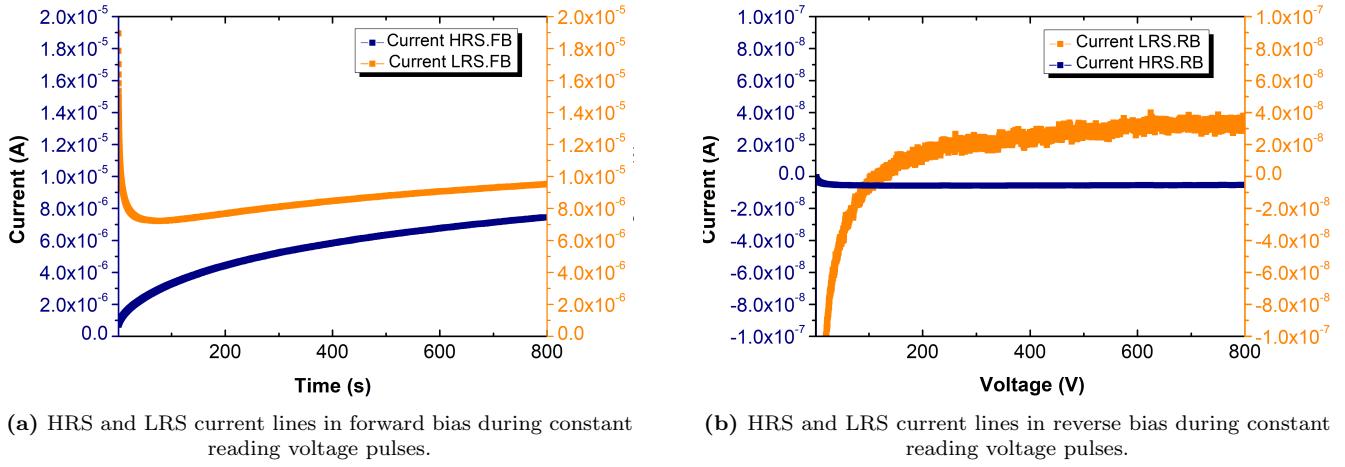

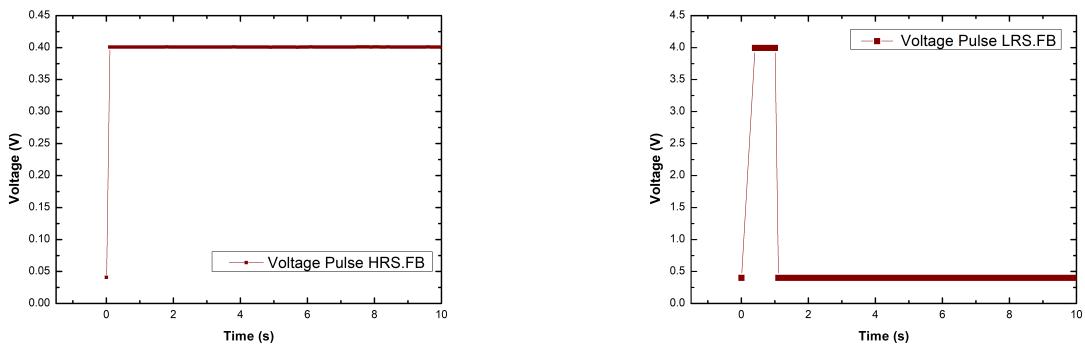

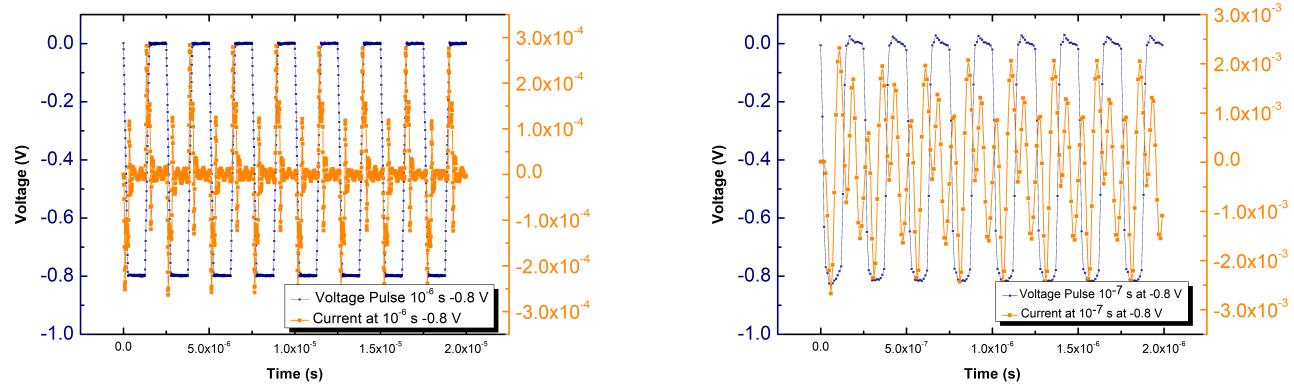

## 4.4 Resistance Changing Rate at Constant Voltage Pulses

Based on the curved traces observed in the I-V sweeps in Section 4.3, along with additional measurements carried out using the I/V List Mode and I/V-t Sampling modes of the Keysight Semiconductor Device

**Figure 4.4.1:** Resulting current at constant reading voltage pulses for each state

Analyzer (see Appendix B.1), it was inferred that the resistance of the Co/Nb:STO devices at constant voltage evolves differently over time depending on the memristive state. To investigate the time dependence on resistance across all memristive states, a series of custom voltage pulses were designed and applied using the WGFMU mode of the Keysight system. These pulses enable selective access to each resistance state while continuously monitoring the output current at a constant applied voltage.

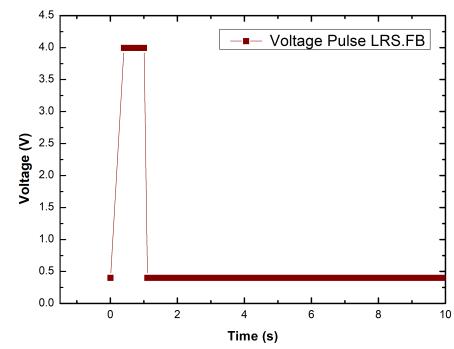

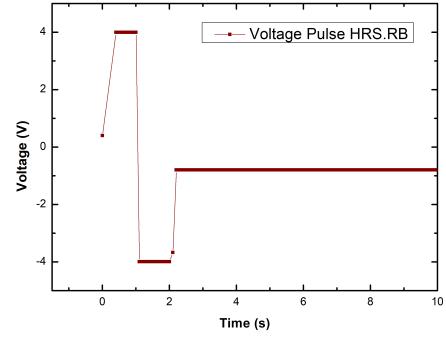

The voltage pulse sequences for each state are shown in Appendix B.1.2. Figure 4.4.1 presents the corresponding current responses for the HRS and LRS under forward bias (B.1.2a and B.1.2b), as well as for the LRS and HRS under reverse bias (B.1.2c and B.1.2d). The voltage pulse sequences applied in each case are, respectively: 0 V  $\rightarrow$  0.4 V, 0 V  $\rightarrow$  2 V  $\rightarrow$  0.4 V, 0 V  $\rightarrow$  2 V  $\rightarrow$  -0.8 V, and 0 V  $\rightarrow$  2 V  $\rightarrow$  -2 V  $\rightarrow$  -0.8 V. Although similar measurements have been performed in previous works by the Spintronics of Functional Materials research group, the pulse durations have been extended in the present study to enhance the quality and depth of the results, allowing for a more thorough discussion [10].

The resulting current under a constant voltage pulse in the HRS under forward bias tends to increase slightly over time, indicating a gradual decrease in resistance (plot B.1.2a). In contrast, the transient current in LRS under forward bias initially exhibits a sudden drop, corresponding to a sharp increase in resistance (plot B.1.2b). However, the current soon begins to increase gradually again, reflecting a progressive decrease in resistance. The slope of the current increase in this phase of the LRS is remarkably similar to that observed in the HRS. Plot 4.4.2a shows both cases on the same graph, where it can be seen that the two curves do not converge but rather run almost parallel to each other.

These voltage pulses aim to simulate the reading process required in memory applications, where a constant voltage must be maintained for a certain duration until the measurement and analysis of the device's output

(a) HRS and LRS current lines in forward bias during constant reading voltage pulses.

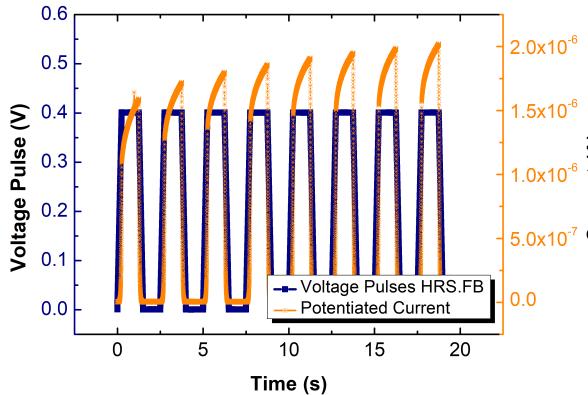

(b) HRS and LRS current lines in reverse bias during constant reading voltage pulses.