WORDT NIET UITGELEEND

# Scheduling in Multi-X a performance evaluation

**Dinand Roeland**

L - 6 OKT. 2000

P. Solversiteit Groningen

Schiutheek

Wiskunde / Informatics / Rekenceminan

Landleven 5

Postbus 800

9700 AV Groningen

RuG

# Scheduling in Multi-X a performance evaluation

**Dinand Roeland**

Rijksuniversiteit Groningen Technische Informatica Postbus 800 9700 AV Groningen

## **Abstract**

This master's thesis project is carried out at Ericsson Utvecklings AB, the research and development centre for Ericsson's Network Core Products. One of the major products of Ericsson Utvecklings AB is the AXE telephone switching system. The need for capacity in AXE switches is increasing at an unexpected rate due to new services like ISDN, GSM and the Internet. To keep up with competition, AXE's central processor's capacity needs to be doubled every third year. A number of projects have been started in order to cope with this problem. One of them is the Gemini project, which will propose an architecture based on commercially available components. One of the main prerequisites for Gemini's new architecture is backward compatibility with existing AXE software. On the long term, the capacity of Gemini's architecture will not be sufficient. The Multi-X project investigates methods of utilising execution on parallel processors, with Gemini's architecture as a premise.

The focus of Multi-X is a new technique called task-level speculative execution. This technique is a form of implicit parallelism; parallelism is extracted from conventional imperative and unmodified code. With speculative execution, assumptions are made on the data and control flow in a program. By looking ahead in the instruction stream, instructions can be run in parallel. Instructions have to be rolled back, i.e. undone, on incorrect assumptions. Instruction-level parallelism is a commonly known technique used in most of today's modern processors. By the beginning of the 1990s, several studies proved the limitations of performance-increase using instruction-level parallelism. These limitations are mainly caused by imperfect predictions of future data and control flow. Since mid 1990s a trend can be observed to not only exploit parallelism at a fine-grained instruction level, but simultaneously also at a coarse-grained task level.

The Multi-X project has developed a prototype to prove the concept of task-level speculative execution on a multiprocessor system based on Gemini's architecture. This prototype is still being improved, tested and modified. No results on performance increase are available yet. As a final phase in Multi-X, the prototype can be optimised in a number of ways. One optimisation is task scheduling, where scheduling is defined as 'the process of deciding what task to execute where and when'. This thesis will focus on the consequences in performance of different task distribution principles.

In this thesis project, the Multi-X prototype is modelled and an optimal scheduling algorithm is defined in order to calculate an upper bound on performance. Furthermore, three practical scheduling algorithms are proposed and a simulator is developed to investigate their performance. Live-recorded telephone switch traffic is used as input data to calculations and simulations. The three proposed practical ways of scheduling are first-come-first-serve scheduling, function-based scheduling and source-based scheduling. With first-come-first-serve scheduling the next task is simply sent to an arbitrary idle processor. This algorithm is currently used in the Multi-X prototype. Function-based scheduling is an attempt to avoid unnecessary rollbacks by examining what functions a task will execute. Source-based scheduling is an attempt to map individual subscribers to individual processors in order to exploit cache-affinity and diminish inter-task dependencies.

The simulations performed in this thesis project are the first on the Multi-X concept where all relevant parameters are taken into account. The concept is proved to hold theoretically, whereas a critical note is made concerning the feasibility of a real implementation. Scheduling should really be seen as an optimisation. Only a moderate performance increase can be accomplished with scheduling. First-come-first-serve scheduling performs very well, even compared to optimal scheduling. Ideas from function-based scheduling can be used additionally to improve performance even more. Source-based scheduling results in poor performance, mainly caused by load imbalance.

A lot of issues remain to be tested, simulated and analysed. This thesis is only one step forward towards a better understanding of a multiprocessor architecture running telephone switch traffic.

Abstract

# **Acknowledgements**

I would like to thank my colleagues at Ericsson Utveckling AB, especially: Lennart Petterson for giving me the opportunity to work on this exciting project; Yusuf Sulaiman for offering a great deal of background knowledge on traffic data; Lars-Åke Johansson for helping me to verify traffic data; and Ruben Rizzi for the interesting and often hilarious conversations during numerous coffee breaks. Also thanks to Marcus Dahlström for providing detailed information on Multi-X and to Nikhil Tikekar for reflections on ideas and concepts.

I would like to thank Professor Ben Spaanenburg at the department of Mathematics and Computing Science, Rijksuniversiteit Groningen, for support and guidance during this project. Special thanks to Nico Kruithof for reviewing this report and for the fruitful co-operation during our studies.

Finally, I am very grateful for the support of my beloved wife Marika and my dear parents. Thank you for helping me to start master studies.

'The fear of the Lord is the beginning of wisdom, and knowledge of the Holy One is understanding.' (Proverbs 9:10)

Dinand Roeland Stockholm, June 2000

Acknowledgements

# **Table of contents**

| Abstract ii          |

|----------------------|

| Acknowledgements iii |

| Table of contents iv |

| List of figures v    |

| List of tables vii   |

| 1 Introduction                                         | 8  |

|--------------------------------------------------------|----|

| 2 Background                                           | 10 |

| 2.1 Problem context                                    |    |

| 2.2 Multi-X as a proposed solution                     |    |

| 2.3 Overview of the Multi-X prototype                  | 10 |

| 2.4 Related work                                       |    |

| 2.5 Thesis project specification                       | 13 |

| 3 Exploring scheduling                                 | 15 |

| 3.1 Definition of scheduling.                          |    |

| 3.2 Learning from other projects                       |    |

| 3.2.1 Similar projects at Ericsson                     |    |

| 3.2.2 Instruction-level parallelism                    |    |

| 3.2.3 Task-level parallelism                           |    |

| 3.2.4 Online transaction processing                    |    |

| 3.3 Position of scheduling in the Multi-X prototype    |    |

| 3.4 Different ways of scheduling for Multi-X           |    |

| 4 Measuring scheduling performance                     | 22 |

| 4.1 How to measure performance parameters              |    |

| 4.2 Finding the right traffic data                     |    |

| 4.2.1 What traffic data is needed                      |    |

| 4.2.2 Where to find traffic data                       |    |

| 4.2.3 Verifying traffic data                           |    |

| 4.2.4 Statistics on used traffic data                  |    |

| 4.3 Modelling the prototype                            |    |

| 4.4 Calculating optimal scheduling                     | 29 |

| 5 Simulation results                                   | 30 |

| 5.1 Optimal scheduling                                 |    |

| 5.2 First-come-first-serve scheduling                  |    |

| 5.3 Function-based scheduling                          |    |

| 5.4 Source-based scheduling                            | 42 |

| 6 Conclusions                                          | 47 |

| 6.1 Evaluation of design decisions                     |    |

| 6.2 Results from measurements                          | 47 |

| 6.3 General conclusions, discussion and future topics  |    |

| References                                             |    |

| Appendix A Collision detection algorithms              | 54 |

| Appendix B Algorithms and proof for optimal scheduling | 56 |

| Annendix C Data on simulation results                  | 62 |

# List of figures

| Figure 1 Relationship between transactions, tasks, functions and messages                                |    |

|----------------------------------------------------------------------------------------------------------|----|

| Figure 2 Architecture of the Multi-X prototype                                                           | 11 |

| Figure 3 Casavant's taxonomy of task scheduling in distributed computing systems                         | 15 |

| Figure 4 Classes of data dependencies                                                                    | 16 |

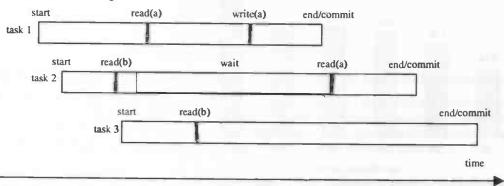

| Figure 5 Two transactions running in parallel                                                            | 18 |

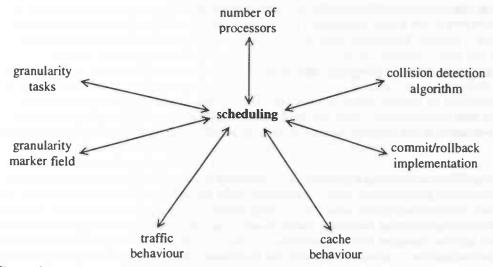

| Figure 6 Relation of scheduling to other parameters in the Multi-X prototype                             |    |

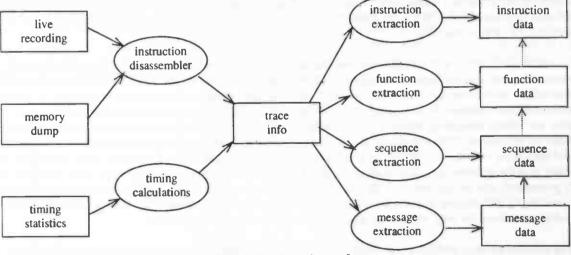

| Figure 7 Data flow in the pre-processing of simulator input data                                         | 24 |

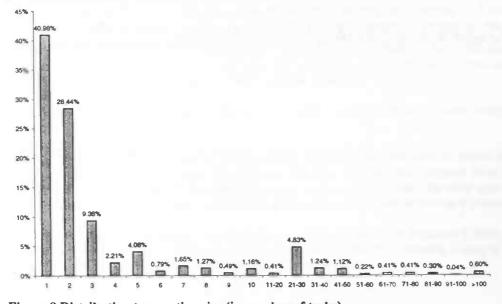

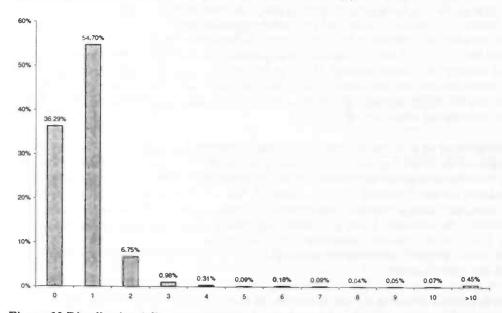

| Figure 8 Distribution transaction size (in number of tasks)                                              | 26 |

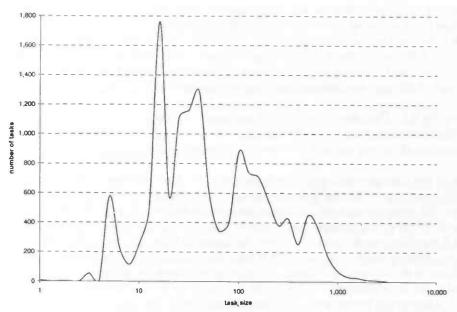

| Figure 9 Distribution of task size (in number of instructions)                                           | 27 |

| Figure 10 Distribution followers per task (in number of tasks)                                           | 27 |

| Figure 11 Waiting time in optimal scheduling                                                             | 29 |

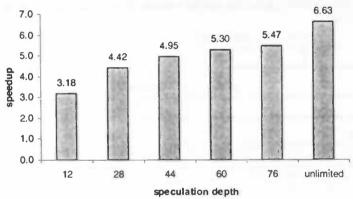

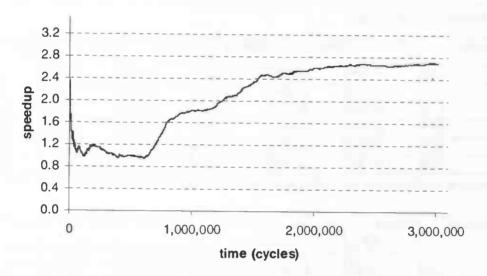

| Figure 12 Speedup for optimal scheduling with Tikekar's algorithm.                                       | 30 |

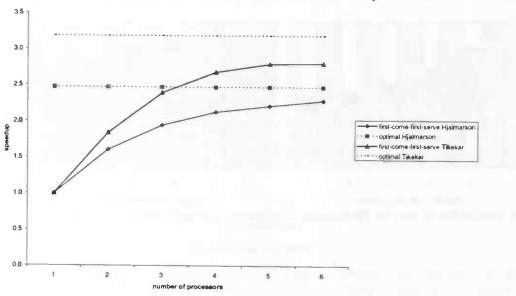

| Figure 13 Comparison first-come-first-serve scheduling for both data collision detection algorithms      | 31 |

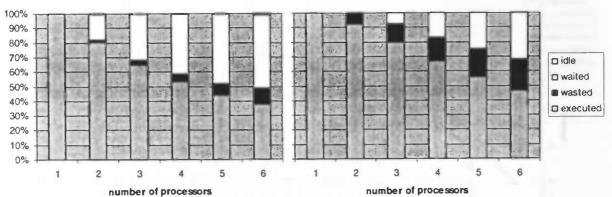

| Figure 14 Distribution of time for Hjalmarson's algorithm (left) and Tikekar's algorithm (right)         | 32 |

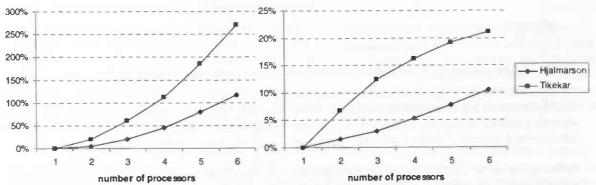

| Figure 15 Rollback frequency (left) and wasted time (right) for both data collision detection algorithms | 32 |

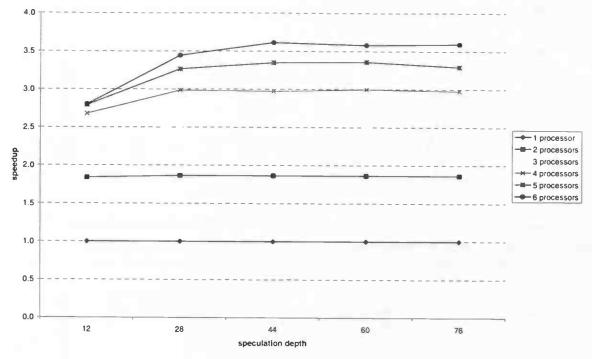

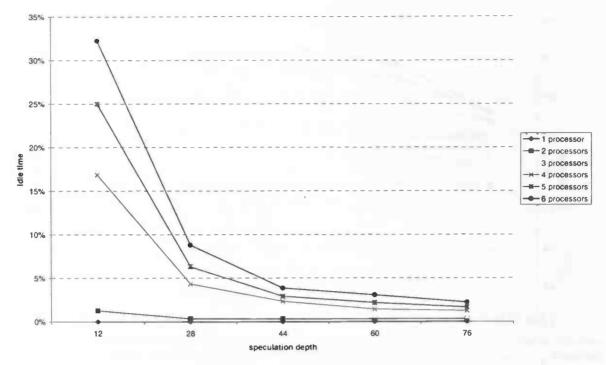

| Figure 16 Speedup as a function of speculation depth                                                     | 33 |

| Figure 17 Idle time as a function of speculation depth.                                                  | 34 |

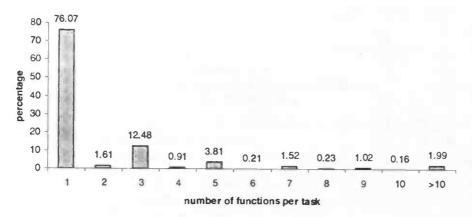

| Figure 18 Distribution of number of functions per task                                                   | 35 |

| Figure 19 Distribution of number of unique functions per task                                            | 35 |

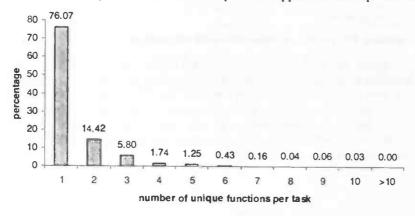

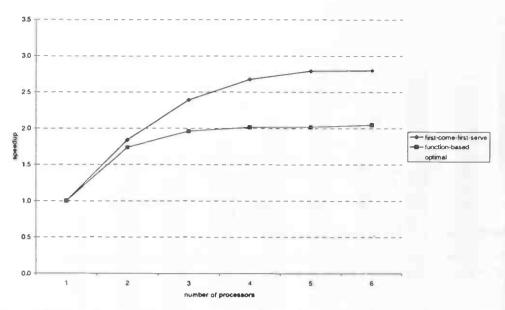

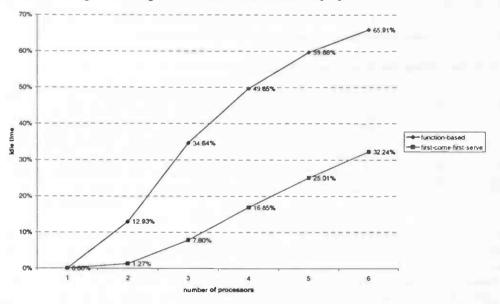

| Figure 20 Comparison of scheduling for Tikekar's algorithm with a speculation depth of 12 tasks          | 36 |

| Figure 21 Comparison idle time Tikekar's algorithm with a speculation depth of 12 tasks                  | 36 |

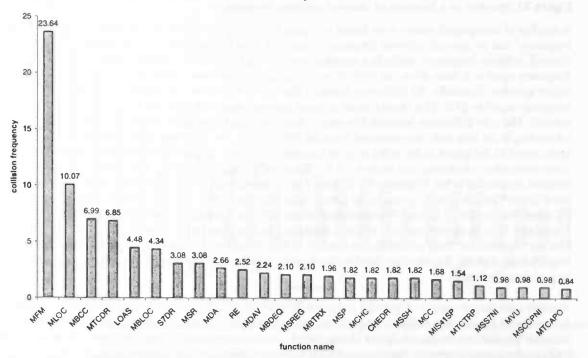

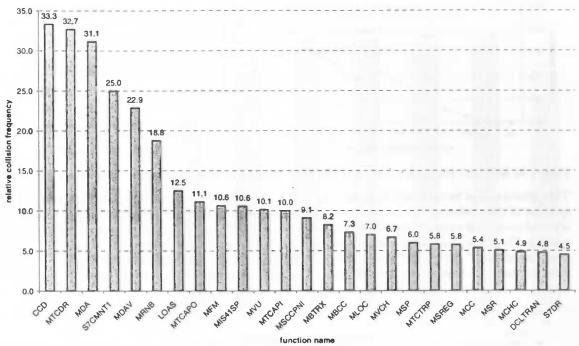

| Figure 22 Collision frequency for functions in recording                                                 | 37 |

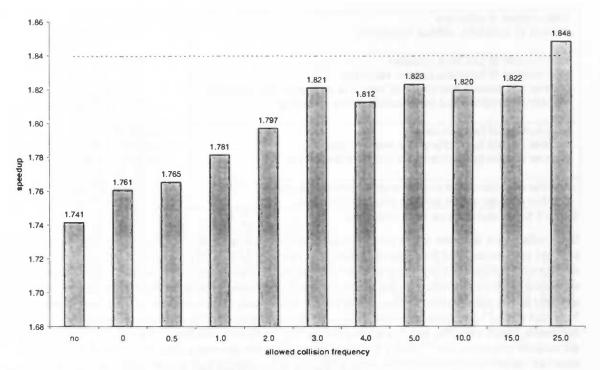

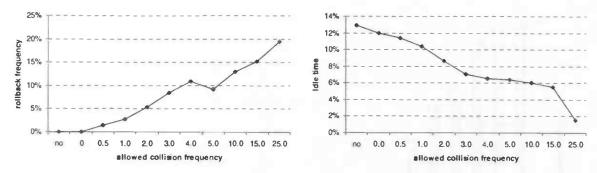

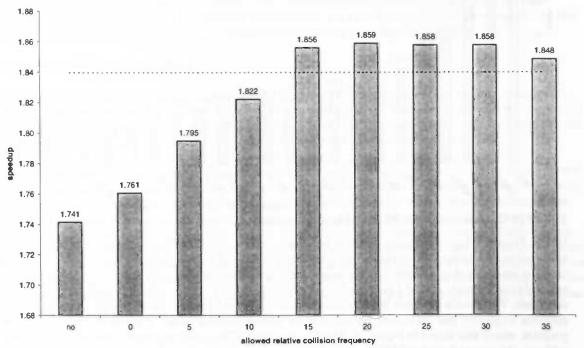

| Figure 23 Speedup as a function of allowed collision frequency                                           | 38 |

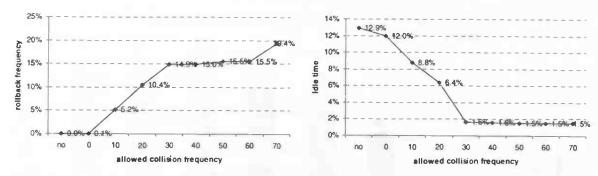

| Figure 24 Rollback frequency (left) and idle time (right) as a function of allowed collision frequency   | 39 |

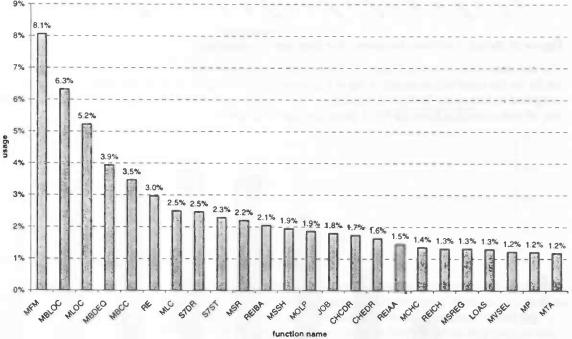

| Figure 25 Distribution of the 25 mostly used functions                                                   | 39 |

| Figure 26 Relative collision frequency for functions in recording.                                       | 40 |

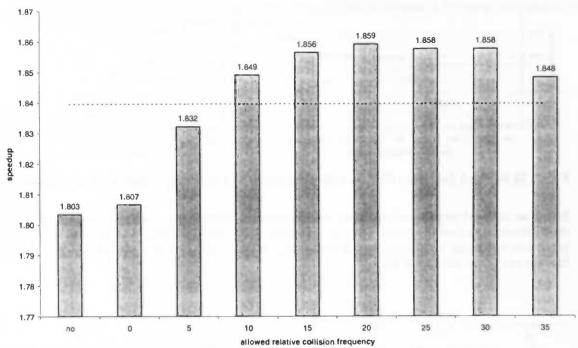

| Figure 27 Speedup as a function of allowed relative collision frequency                                  | 40 |

| Figure 28 Rollback frequency (left) and idle time (right) as a function of relative collision frequency  | 41 |

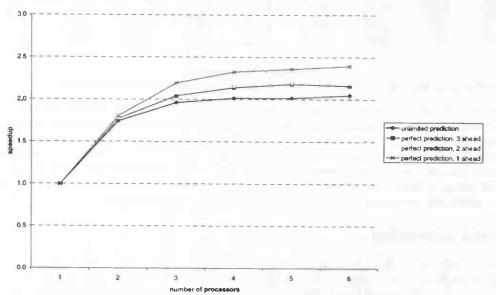

| Figure 29 Function-based scheduling with limited prediction                                              | 41 |

| Figure 30 Speedup as a function of allowed relative collision frequency with no prediction               | 42 |

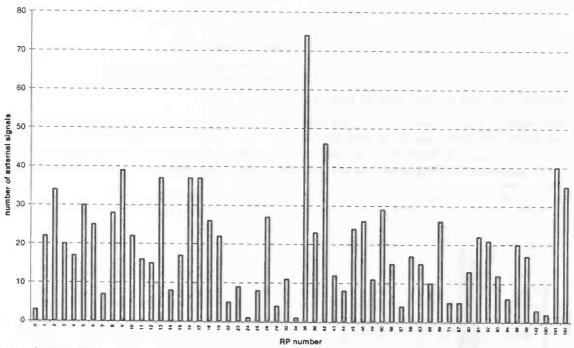

| Figure 31 Distribution of external signals from remote processors                                        | 43 |

| Figure 32 Speedup for source-based scheduling                                                            | 44 |

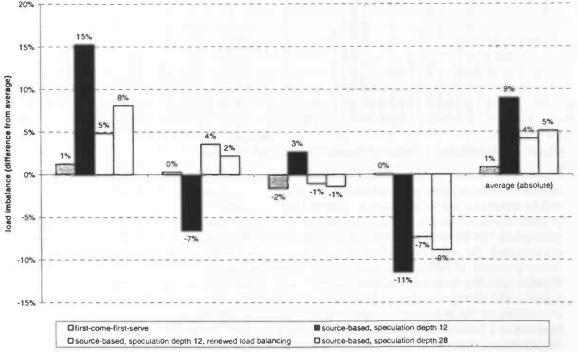

| Figure 33 Load balancing for source-based scheduling compared to first-come-first-serve for 4 processors | 44 |

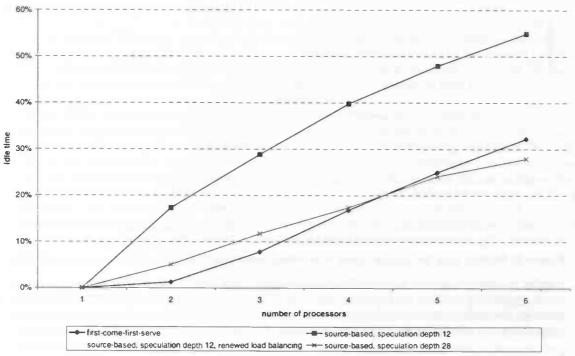

| Figure 34 Idle time for source-based scheduling compared to first-come-first-serve scheduling            | 45 |

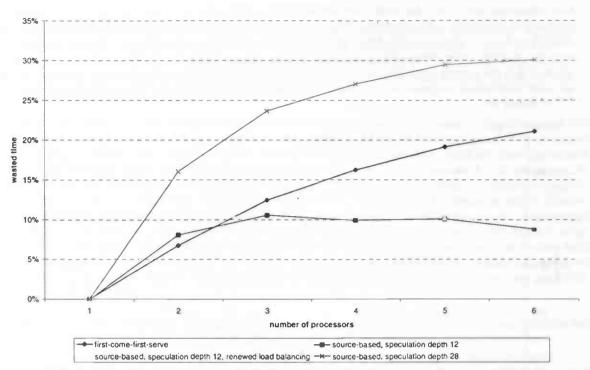

| Figure 35 Wasted time for source-based scheduling compared to first-come-first-serve scheduling          | 46 |

| Figure 36 Marker field for Hjalmarson's algorithm                                                        | 54 |

| Figure 37 Marker field for Tikekar's algorithm.                                                          | 55 |

| Figure 38 Tikekar's data collision detection algorithm                                                                   | 55 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| Figure 39 Hjalmarson's data collision detection algorithm                                                                | 56 |

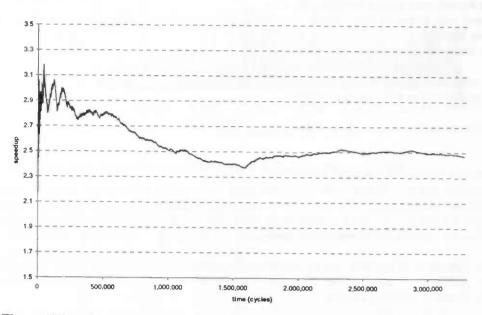

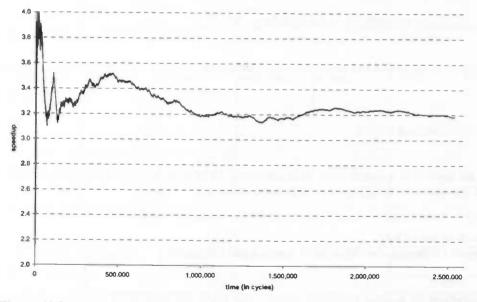

| Figure 40 Speedup in time for optimal scheduling with Hjalmarson's algorithm                                             | 62 |

| Figure 41 Speedup in time for optimal scheduling with Tikekar's algorithm, speculation depth 12                          | 62 |

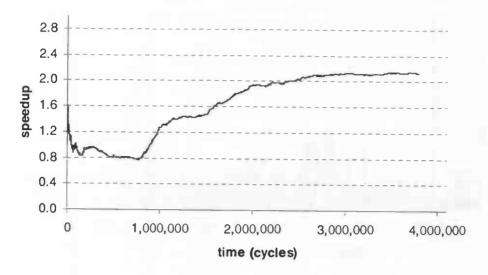

| Figure 42 Speedup in time for first-come-first-serve scheduling, Hjalmarson's algorithm, 4 processors                    | 63 |

| Figure 43 Speedup in time for first-come-first-serve scheduling, Tikekar's algorithm, speculation depth 12, 4 processors | 63 |

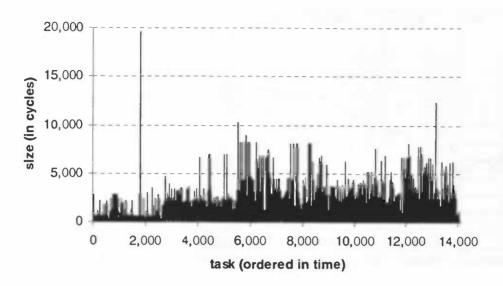

| Figure 44 Task, ordered at position in input data, in number of cycles                                                   | 64 |

List of figures

# List of tables

| Table 1 Features of architectures using speculative execution                                                                                                | 13 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2 Some statistics on the pre-processed data                                                                                                            | 26 |

| Table 3 Some statistics on data collisions                                                                                                                   | 37 |

| Table 4 Some statistics on operating system transactions                                                                                                     | 43 |

| Table 5 Data collision detection algorithm at writing                                                                                                        | 54 |

| Table 6 Data collision detection algorithm at reading                                                                                                        | 54 |

| Table 7 Action table for writing                                                                                                                             | 55 |

| Table 8 Action table for reading                                                                                                                             | 55 |

| Table 9 Results first-come-first-serve scheduling with Hjalmarson's algorithm                                                                                | 64 |

| Table 10 Results first-come-first-serve scheduling with Tikekar's algorithm at a speculation depth of 12                                                     | 64 |

| Table 11 Results first-come-first-serve scheduling with Tikekar's algorithm at a speculation depth of 28                                                     | 64 |

| Table 12 Results first-come-first-serve scheduling with Tikekar's algorithm at a speculation depth of 44                                                     | 65 |

| Table 13 Results first-come-first-serve scheduling with Tikekar's algorithm at a speculation depth of 60,                                                    | 65 |

| Table 14 Results first-come-first-serve scheduling with Tikekar's algorithm at a speculation depth of 76                                                     | 65 |

| Table 15 Results function-based scheduling with Tikekar's algorithm, speculation depth 12, perfect prediction                                                | 65 |

| Table 16 Results function-based scheduling with collision frequency, Tikekar's algorithm, speculation depth 12, perfect prediction                           |    |

| Table 17 Results function-based scheduling with relative collision frequency, Tikekar's algorithm, speculation depth 12, perfect prediction                  |    |

| Table 18 Results function-based scheduling with Tikekar's algorithm, speculation depth 12, perfect prediction, 3 ahead                                       |    |

| Table 19 Results function-based scheduling with Tikekar's algorithm, speculation depth 12, perfect prediction, 2 ahead                                       |    |

| Table 20 Results function-based scheduling with Tikekar's algorithm, speculation depth 12, perfect prediction, 1 ahead                                       |    |

| Table 21 Results function-based scheduling with relative collision frequency, Tikekar's algorithm, speculation depth 12, perfect prediction 1 function ahead | 67 |

| Table 22 Results source-based scheduling with Tikekar's algorithm, speculation depth 12                                                                      |    |

| Table 23 Results source-based scheduling with Tikekar's algorithm, speculation depth 12, improved load balancing                                             |    |

| Table 24 Results source-based scheduling with Tikekar's algorithm, speculation depth 28                                                                      |    |

## 1 Introduction

This thesis is on speeding up sequential programs by parallelising them. Probably ever since the introduction of the Von Neumann architecture, people have been trying to overcome the strictly sequential execution imposed by this architecture. In 1967, Amdahl [2] argued not to have too high expectations on parallelising sequential programs by introducing a very straightforward paradigm. If N is the number of processors, s is the amount of time spent (by a serial processor) on serial parts of a program and p is the amount of time spent (by a serial processor) on parts of the program that can be done in parallel, then the potential speedup is given by Equation 1.

$$Speedup = \frac{s+p}{s+\frac{p}{N}} = \frac{1}{s+\frac{p}{N}}$$

#### Equation 1 Amdahl's law

Even when using an infinite amount of processors, the maximal speedup is bound to s<sup>-1</sup>. Although criticised later [21], Amdahl's law does point out that truly big gains in parallel programming can only be achieved by reducing serial bottlenecks.

The question remains how to exploit parallelism from a sequential program. The easiest way, from a computational point of view, is to push the burden on the programmer and force him to (re-)state the problem in a parallel program. This is called *explicit parallelism*. Another way is to use paradigms such as functional or logic programming where a compiler can readily generate parallel code [40]. This thesis considers *inherent parallelism* or *implicit parallelism*, that is, parallelism from conventional imperative programs, which have not been explicitly modified to extract parallelism. The drive for inherent parallelism comes from a number of directions. Firstly, the great majority of the world's code is written in imperative languages and it seems almost inconceivable that it could all be rewritten to explicitly take advantage of parallelism. Secondly, it is now difficult to take advantage of and keep busy the number of transistors available on modern CPU chips without making some use of parallelism. Thirdly, at some point in the next decade or two Moore's law will fail and the steady exponential increase in performance of silicon based computers will cease. Parallelism will then be needed to maintain performance increases [8].

Extracting inherent parallelism can be done at compiler-time, at run-time or both. Run-time techniques include out-of-order execution, register renaming, alias renaming, branch prediction and multiple-path execution. The processor can look ahead during execution and execute instruction out-of-order and in parallel, provided no logical inconsistencies arise as a result of doing so. With register renaming, the processor removes storage conflicts by providing additional registers to re-establish the correspondence between registers and values. The additional registers are allocated dynamically by hardware, and the registers are associated with the values needed by the program. Alias analysis is like register renaming, but for memory locations. Branches impede the ability of the processor to fetch instructions because they make instruction-fetching dependent on the result of instruction execution. When the outcome of a branch is not known, the instruction fetcher is stalled, reducing the chances that the processor can find instructions to execute in parallel. To overcome this problem, the outcome of a branch can be predicted. Branch prediction [58] can be done dynamically by hardware or statically by annotating the program with prediction information during compile-time. Until the true outcome of the branch is known, instructions on the predicted path can be executed speculatively. When using speculative execution, these instructions have to be undone (by performing a rollback) if the assumption was incorrect. Another way to avoid the impediments of branches is to have the processor pursue both paths at a branch. This technique is called multiple-path execution; the processor can simply discard the results of the incorrect path. Since branches happen quite often in normal code, we may encounter another branch before we have resolved the previous one. In order not to use up all machine resources, multiple-path execution and branch prediction can co-operate to achieve good results. Extracting inherent parallelism at compiler-time is based on a static analysis of the code to execute. Using this analysis, the instructions can be (re-) scheduled. Here, scheduling can be defined as the process of arranging the order of instructions in object code so that they are executed by hardware in an optimum order. A common scheduling technique is loop unrolling. When a loop is unrolled, the instructions for two or more loop iterations are written explicitly. This gives the processor a larger scope to look ahead and execute instructions in parallel. Techniques to extract inherent parallelism at a fine-grained instruction-level are also known under the common name of instruction-level parallelism [31, 70, 71]. Most of the techniques mentioned here were discussed in the classic article "Look-Ahead Processors" by Keller in 1975 [34].

Introduction

In the beginning of the 1990s, several studies [37, 70] proved the limitations of instruction-level parallelism. Using only fine-grained techniques, the speedup tends to be limited to a factor of approximately ten. The reason for this is that instruction-level parallelism relies heavily on good branch prediction algorithms. Even if prediction algorithms have a 90% accuracy [31, 49], this will only leave 60% after five speculative branches. In typical programs one in seven instructions is a branch [25], which does not leave much scope for extracting parallelism. Because of this limitation and the ever-growing amount of transistors on processor chips, a trend can now be observed to not only exploit parallelism at a fine-grained level, but also at a coarse-grained level [10, 61, 63]. This is called *task-level parallelism* or *thread-level parallelism*.

Several architectures for extracting task-level parallelism have been proposed, including Multiscalar Processors of the University of Wisconsin-Madison [59], the Superthreaded Processor Architecture [67], the WarpEngine of the University of Waikato [9], Stanford's Hydra [48], MIT's M-Machine [20] and the Simultaneous Multithreading architecture [69]. It is here where Ericsson's Multi-X prototype comes in. This thesis is a part of the Multi-X project. The next chapter describes the background of the Multi-X project and specifies the focus of this thesis project.

Introduction

## 2 Background

Ericsson Utvecklings AB is the research and development centre for Ericsson's Network Core Products. One of the products of Ericsson Utvecklings is the AXE telephone switching system. AXE is the world's most deployed communication architecture with 130 million lines in service in some 125 countries. This thesis project has been done at the System Processors department, that is responsible for the research and development of AXE's central processor system called APZ CP. The latest version available on the market is the APZ 212 30 [28].

This chapter describes the context of this thesis project. The first section outlines the capacity problem Ericsson faces today. The next section introduces Multi-X as one of the solutions to this problem. Section three gives a general overview of the Multi-X prototype and the succeeding section describes related prototypes. The last section of this chapter specifies the goal for this thesis project.

#### 2.1 Problem context

Due to new services like GSM, ISDN and Internet, the need for capacity in the APZ CP is increasing at a previously unexpected rate. To keep up with competition, APZ's capacity needs to doubled every three years. In order to cope with this problem, a number of projects have been started. One of these is the *Gemini* project. Until now, Ericsson itself designs all hardware (ASICs). The Gemini project proposes an architecture based on commercially available components. This way, a number of design problems can be pushed onto external suppliers like Compaq, SUN or Intel. It will also give Ericsson designers more flexibility when designing new versions of the APZ CP. An enormous amount of software has been written for earlier versions of the APZ CP. Therefore, Gemini's new architecture is backward compatible. No modifications in existing code are allowed. A virtual machine is used to fit existing code into the new architecture. Both the latest version of the APZ CP and the proposed architecture by Gemini are single processor architectures executing code sequentially, but exploiting instruction-level parallelism internally.

## 2.2 Multi-X as a proposed solution

It has been proved that there is a significant amount of task-level parallelism to be exploited in APZ CP code, which might lead to an increase in performance (conform Amdahl's law) [62, 72]. The proposed method to exploit this parallelism is task-level speculative execution. Within the Multi-X (Multiple Executor) project, methods of utilising execution on parallel processors are investigated. More specifically, Multi-X has been started in order to evaluate and demonstrate techniques based on task-level speculative execution and resource locking [51, 52]. Multi-X will be based on the (expected) results of Gemini. This way, the performance of unmodified APZ CP code will increase while using commercially available hardware components. Like speculative execution on an instruction level, speculative execution on a task-level will be limited by the intrinsic features of the existing code that has been written with a single sequential processor in mind [72]. Therefore, the Multi-X project has to be seen as a first step in the architectural evolution from a single processor and sequential programs towards multiple processors and explicitly parallelised programs [65]. The Multi-X project is carried out in co-operation with Chalmers University of Gothenburg [6].

Two projects within Ericsson that have involved parallel processing are CMC and Tor. The former resulted in an architecture for which existing software had to be modified. The costs for implementation would have been too high. Trying to overcome these problems, a number of projects have been started. One of them is Multi-X. The latter has even investigated speculative execution but was cancelled because of a strategic change to build a future architecture on commercially available components.

## 2.3 Overview of the Multi-X prototype

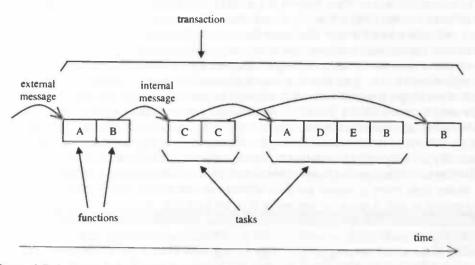

The APZ CP can be seen as an online transaction processing system. The structure of an APZ CP transaction is visualised in Figure 1. Transactions can be divided into one or more uninterrupted sequences of program functions. Such a sequence will be called transaction task or simply task. A function is an uninterrupted sequence of instructions, as in imperative programming languages. Transactions are started by an external message. These messages originate from one of the remote processors (RP), which handle events (e.g. the starting of a phone call). A task is initiated by a message and the executions of a task might give rise to one or more internal messages. We define the tasks started by these messages to be the followers of the initiating task. A message includes the address of the first function to be executed and data parameters [16, 17].

Figure 1 Relationship between transactions, tasks, functions and messages

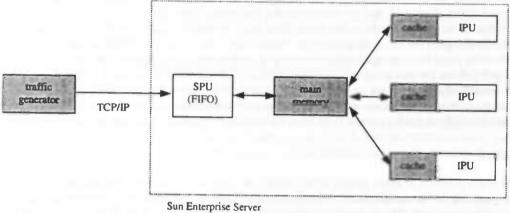

Figure 2 gives an overview of the Multi-X architecture. A traffic generator simulates external events. The signalling processor unit (SPU) administers all messages, both external and internal, in a first-in-first-out (FIFO) message queue. Tasks are executed by assigning a message to an instruction processor unit (IPU). IPUs exploit instruction-level parallelism. Main memory is shared, while every IPU has its own cache. Except for the number of IPUs, the Multi-X prototype resembles the architecture of the existing APZ CP. This way, the restriction not to change existing code can be met more easily. The prototype is implemented on a Sun Enterprise Fileserver with four processors; three of these are used as an IPU.

Figure 2 Architecture of the Multi-X prototype

In the proposed Gemini architecture (and therefore also in the Multi-X architecture), functions are written in the PLEX-C language, which is specifically designed for telecommunication exchanges. PLEX-C code is compiled into ASA assembly code for the APZ CP. ASA code is interpreted by a virtual machine (AXE VM) in order to run existing code on a new architecture based on commercially available components [18, 28, 51].

In the initial phase of the Multi-X prototype, resource locking without speculative execution was investigated. This proved not to increase performance [72, 73], and speculative execution was included in the Multi-X prototype. The next task is simply assigned to an idle IPU, assuming no data collisions will occur. This is called data speculation and implies the execution of an instruction before the execution of a preceding instruction on which it may be or is data dependent. Control speculation, e.g. branch prediction, implies the execution of an instruction before the execution of a preceding instruction on which it is control dependent [41]. To date, the Multi-X prototype only supports data speculation. Speculation is done blindly; no predictions are made whether

<sup>&</sup>lt;sup>1</sup> For optimisation reasons, most code will eventually be (JIT-) compiled. However, conceptually, ASA code is still interpreted.

speculations will be successful or not. When inserted in the FIFO, every task receives a task number<sup>2</sup>. All common data areas have a marker field, containing the numbers of the tasks that have lastly read or written the data area. Common variables are global only within one function, conform static variables in C. To access variables in another function, internal messages have to be used (conform methods in C++). In ASA code, there are basically three types of common variables: 1) single variables, e.g. an integer; 2) single arrays, a collection of elements of one single variable; 3) arrayed structure, where a structure is a set of single variables and single arrays. In the Multi-X prototype, every element of an arrayed structure has one marker field and every single variable and single array have one marker field. By comparing the marker field with the number of the executing task on every read or write, data collisions can be detected. On collision, one or more tasks are rolled back. When completed, a task is ready to be *committed*, i.e. all modifications made by this task to common variables are made permanent. By allowing only the oldest task to be committed, the original sequential execution order is preserved (*in-order commit*). Messages originating from a task are not inserted in the FIFO until the task has been committed. At any time, every processor executes at most one task and no other task is started on a processor until the executing task is ready for commit or is rolled back [26, 56].

Performing commits and rollbacks might be implemented in different ways [27]. One way is to carry out data modifications directly in the actual memory location after having copied the original contents to a temporary area. Another way is to copy data from the actual memory into a separate memory to read from and write to. The first way is called the *original method* and will result in relatively fast commits but slow rollbacks. The second way is called the *temporary method* and will result in slow commits but fast rollbacks. At this moment, Multi-X uses the original method.

Two collision detection algorithms have been proposed. The first was proposed by Hjalmarson [26] and allows only one speculatively executed read or write per common data area at any time. If more are requested, the youngest task waits. If data collision is detected, a rollback on the colliding task(s) and all younger tasks is performed. The marker fields contain one field for the number of the task that has lastly written the data area and one field for the number of the task that has lastly read the data area. These fields are reset at initialisation and at rollback or commit of the task assigned to that field. The total number of uncommitted tasks is virtually unlimited. Tikekar designed the second algorithm at a later stage. This algorithm is more aggressive (i.e. avoids waiting) by allowing more than one speculatively executed read or write per common data area at any time. The speculation depth defines the maximum number of speculatively executed data accesses. At any time, the number of uncommitted tasks does not exceed the speculation depth. This way, the size of the marker fields is linear with the speculation depth. Moreover, the algorithm prevents unnecessary rollbacks. Both algorithm are often referred to throughout this report and have been included in "Appendix A Collision detection algorithms".

#### 2.4 Related work

As mentioned in the previous chapter, several other projects attempt to exploit both instruction-level parallelism and task-level parallelism. All architectures mentioned here are, like the Multi-X prototype, multiprocessor systems with a shared memory. The *M-Machine* [20, 33] and the *Simultaneous Multithreading* architecture [69] exploit instruction-level parallelism by statically scheduling independent instructions to be executed simultaneously on independent functional units of a processor. Task-level parallelism is exploited by dynamically interleaving the instruction streams of several processors in order to utilise unused functional units. These architectures rely heavily on hardware synchronisation mechanisms and compile-time program transformations. Neither architecture uses some form of speculative execution.

In the Multiscalar Processors approach [29, 41, 59], a sequential program is statically represented as a control flow graph. The nodes are basic blocks (tasks) and arcs from one node to another represent the flow of control. A sequencer speculates which task will be executed next and assigns this task to the next free processing unit. On mis-speculation, a rollback will be performed on that task and all its successors. To facilitate sequential semantics, tasks commit in the same order as they are assigned to processing units. Within a task, data values might be speculated and a unidirectional ring between the processing units is used to forward computed data values from the oldest to the youngest task. The Superthreaded Processor Architecture [67] is similar to the Multiscalar architecture, but does not include data speculation. As a result, less memory resources are needed for administration. The WarpEngine [8, 9] organises up to 16 instructions into one task. Speculative execution on

Background

<sup>&</sup>lt;sup>2</sup> In the current implementation of the Multi-X prototype, a task is not assigned a number until its message is extracted from the FIFO. Since only the oldest message is extracted at any time, this is conceptually the same as assigning a number when inserting a message.

control or data selects complete tasks for execution. Each task is dynamically allocated a time stamp when it is scheduled for execution. This time stamp is used for all read and write requests issued from within the task. The time stamps impose a single linear temporal order relating all the reads and writes. The way this is done is to associate with each block an interval of time and to allow it to schedule a number of child tasks. The intervals of the children are disjoint and contained within the parent interval. All the time intervals form a tree and a sequential execution of a program will consist of a pre-order traversal of this tree. Rollback of instructions is initiated when the memory returns a revised value from a read. Only instructions (and children) dependent on the revised value have to be rolled back and re-executed. Hydra [24, 47, 48] is targeted for multiple threads, originated from multiple programs or a single compiler-annotated program. Hydra is influenced by the Multiscalar approach, but focuses on the parallelisation of loop iterations. Speculation is mainly on data, using data forwarding techniques like Multiscalar. Control speculation is minimised by placing a larger demand on the compiler to divide programs in tasks and by introducing some run-time software control. Table 1 summarises a number of features of the architectures mentioned.

| Architecture  | Target                       | Speculation         | Support                                                                               | Commit                                                     | Rollhack                                                   | Scheduling                                   |

|---------------|------------------------------|---------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------|

| Multiscalar   | single sequential program    | control and<br>data | compile-time<br>transformations,<br>run-time hardware                                 | in-order                                                   | task and all its<br>successors                             | next task to next<br>free processing<br>unit |

| Superthreaded | single sequential program    | control             | compile-time<br>transformations,<br>run-time hardware                                 | in-order                                                   | task and all its<br>successors                             | next task to next<br>free processing<br>unit |

| WarpEngine    | single sequential<br>program | control and<br>data | run-time hardware,<br>compile-time<br>transformations<br>suggested as<br>optimisation | in-order, out-<br>of-order<br>suggested as<br>optimisation | partial rollback<br>only instructions<br>directly affected | heuristics using<br>time stamp               |

| Hydra         | multiple threads             | data                | compile-time<br>transformations,<br>run-time hardware,<br>run-time software           | in-order                                                   | per task                                                   | round-robin in<br>loop iteration             |

| Multi-X       | online<br>transactions       | data                | run-time software                                                                     | in-order                                                   | task and all<br>newer tasks                                | next task to next<br>free processing<br>unit |

Table 1 Features of architectures using speculative execution

Compared to architectures using speculation, Multi-X is unique in a number of ways. Firstly, the Multi-X prototype is targeted specifically for online transaction processing, not for sequential or multi-threaded programs. The dynamic behaviour of online transactions makes static analysis difficult. Secondly, the Multi-X prototype as proposed so far is a run-time software-only approach. The restriction on using only commercially available component implies no hardware support for speculative execution. The restriction on unmodified code implies no compile-time support.

The Hydra approach resembles the Multi-X prototype best. This architecture is able to speedup online transaction processing by a factor three compared to a single processor [23]. Unfortunately, Hydra research focuses on loop constructs, which are rare in APZ CP code. However, the techniques used are also applicable to exploit method-level parallelism. In method speculation, sequential method invocations in object-oriented programs are mapped onto speculative tasks that are executed in parallel with the in-order thread. This does resemble Multi-X task invocation by messages more accurately. An empirical study proves method speculation to be able to speedup Java programs by a factor of approximately two [7].

A number of products have emerged from the research architectures mentioned above. One is a new compiletime loop parallelisation technique for Java programs [32]. Two processors exploiting task-level parallelism by speculation are Sun's MAJC architecture [64] and NEC's MP98 [43]. A feasibility study on the use of these processors is conducted in the Multi-X project.

### 2.5 Thesis project specification

The Multi-X prototype might be optimised in a number of ways. One optimisation proposed to analyse the functions' code statically and extract parts that certainly can be executed in parallel. This approach alone, however, proved no substantial performance gains [12].

Another way to optimise the performance of the Multi-X prototype is to modify existing parameters; e.g. the collision detection algorithm, the granularity of tasks, the granularity of the marker area, the cache coherence

Background 13

protocol or the task scheduling. It is unknown to what extent these parameters influence the overall performance and how they are co-related. The task numbering needed for the proposed collision detection algorithms impose a too strict order on the tasks. Allowing tasks to be committed out-of-order might also give some performance gains. Rollback and commit is done per task, but the task granularity might also be defined as a single function or a complete transaction (see Figure 1). Collision detection is based on marker areas, which are now defined as single variables, single array or an element of an arrayed structure. Other granularities are possible; e.g. a number of related variables. Caches are known to influence performance substantially, and different cache coherence protocols might influence the overall performance of the Multi-X prototype. This is investigated in a master thesis project [53] carried out in parallel with this master thesis project.

This thesis will focus on the consequences of different task distribution principles, also called *task scheduling*. A preliminary survey has been done, resulting in six straightforward distribution principles [30]. The goal of this thesis is to gain a more profound understanding of how scheduling influences the overall performance of the Multi-X prototype; i.e.: how does scheduling relate to other parameters in the Multi-X prototype and what is its importance?; how can tasks be scheduled?; what performance can we expect from different ways of scheduling? In the next chapters, concepts will be defined more clearly and the questions mentioned above will, at least partly, be answered.

The next chapter explores scheduling, starting with definitions and a summary of scheduling in other projects. The last two sections focus on scheduling in Multi-X and define a number of scheduling algorithms to investigate. Chapter 4, "Measuring scheduling performance" defines how the performance of the proposed scheduling algorithms will be measured. The succeeding chapter presents measurement results and this report ends with conclusions in chapter 6.

Background 14

# 3 Exploring scheduling

In this chapter, scheduling as a whole is explored, starting with general definitions and ending with Multi-X specific proposals. The first section gives a theoretical framework on scheduling. The second section explores scheduling solutions proposed by related projects. Section three defines the position of scheduling in Multi-X, in order to propose a number of relevant scheduling methods in the last section.

## 3.1 Definition of scheduling

If a task is generally defined as an uninterrupted sequence of program functions or instructions, then scheduling can be defined as 'the process of deciding what task to execute where and when'3. Scheduling decisions are made on (dynamic) properties of the objects to be executed or on (dynamic) properties of the environment in which the objects are executing. The goal of scheduling is to improve performance (e.g. the total execution time) by minimising one or more costs (e.g. the number of cache misses in cache-affinity scheduling [68] or the number of missed deadlines in real-time environments [1]).

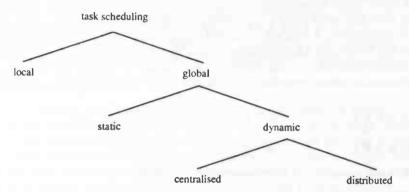

A large number of scientific papers have been written on scheduling, a lot of them introducing a new way of scheduling to minimise some specific cost for some specific environment. Casavant [5] proposes a taxonomy of scheduling in distributed computing systems. Figure 3 is an abstract of this taxonomy.

Figure 3 Casavant's taxonomy of task scheduling in distributed computing systems

Local scheduling is involved with the assignment of processes to the time-slices of a single-processor system. Global scheduling is the problem of deciding where to execute a process, and the job of local scheduling is left to the operating system. Given perfect information at compile-time about the execution time and the memory referencing behaviour of the individual tasks, a static scheduling strategy can pre-compute an optimal schedule. Since all scheduling decisions are made at compile-time, there is no run-time overhead associated with static scheduling. In many applications, however, the necessary information is not available at compile time, which may lead to sub-optimal performance. To compensate for this lack of a priori information, dynamic scheduling postpones the assignment of tasks to processors until the program is executing. Scheduling decisions are then adjusted to match the dynamically changing conditions encountered at run-time. Centralised and distributed dynamic scheduling strategies have been proposed. Typically, the distributed strategies spread the scheduling operation over the processors so that idle processors assign work to themselves from a central or distributed queue of available tasks. The centralised strategies consider storing global information at a centralised location and use this information to make more comprehensive scheduling decisions. To do this, they use one or more dedicated processor's computing and storage resources. A major issue to take into account in designing distributed or centralised dynamic scheduling algorithms is the overhead associated with executing such algorithms. In many of the existing techniques, the time required to perform this scheduling adds directly to the total program execution time [22].

<sup>&</sup>lt;sup>3</sup> Note that scheduling is not restricted to one level. Within a task, instructions might be (re-) scheduled. See also the definition of scheduling in chapter 1, "Introduction".

## 3.2 Learning from other projects

Before going deeper into scheduling targeted specifically for Multi-X, it is interesting to see what other projects have achieved on this topic. In order to relate as much as possible to the Multi-X prototype, four areas have been investigated: 1) scheduling in similar projects at Ericsson; 2) scheduling in instruction-level parallelism; 3) scheduling in task-level parallelism; 4) scheduling in online transaction processing.

#### 3.2.1 Similar projects at Ericsson

The only project conducted at Ericsson similar to Multi-X is the Tor project [50]. This project had the same premises as Multi-X, but was a hardware-only approach. The Tor project did not provide any new ideas on scheduling. The scheduling algorithm used was the same as the initial scheduling algorithm in the Multi-X prototype; the next task in the queue is simply sent to an idle IPU. No other ways of scheduling have been investigated.

#### 3.2.2 Instruction-level parallelism

Scheduling for instruction-level parallelism [25, 31, 42, 70, 71] deals with distributing a single instruction stream among the processor's functional units and reordering instructions. Scheduling is constrained by data and control dependencies. Data dependencies can be divided into four groups. For true data dependencies, the result of the first instruction is an operand of the second. These are also called read after write (RAW) dependencies. The second group is anti-dependencies, where the first instruction uses the old value in some location and the second sets that location to a new value. These dependencies are also called write after read (WAR). Instructions have an output dependency or a write after write (WAW) dependency, if both instructions assign a value to the same location. The last group of dependencies is read after read (RAR) dependencies, where two instructions read from the same location. WAR, WAW and RAR dependencies are false data dependencies and can be resolved using register renaming and alias analysis (see also chapter 1, "Introduction"). There is a control dependency between a branch and an instruction whose execution is conditional on it. Branch predictors can partially resolve control dependencies.

$$\begin{array}{lll} r_1 := f(\ r_3\ ) & r_2 := f(\ r_1\ ) & r_1 := f(\ r_2\ ) & r_2 := f(\ r_1\ ) \\ \dots & \dots & \dots & \dots \\ r_2 := f(\ r_1\ ) & r_3 := f(\ r_1\ ) & r_1 := f(\ r_3\ ) & r_1 := f(\ r_2\ ) \\ \end{array}$$

$$\begin{array}{lll} RAW \ dependency & RAR \ dependency & WAW \ dependency & WAR \ dependence & WAR \ d$$

#### Figure 4 Classes of data dependencies

At compile-time, a sequential program can be divided into basic blocks. A basic block is a code sequence that does not contain a branch or a branch target, except at the beginning or at the end. Scheduling such code sequences is easy, since we know that every instruction in the block is executed if the first one is. We can simply make a graph of the dependencies among the instructions and order the instructions so as to minimise the stalls. The critical path of such a graph is that path with the minimum execution time of the entire sequence – no amount of instruction concurrency can make the execution time shorter. The critical path places a lower bound on the execution time and identifies the operations that determine this execution time. The optimal scheduling can be calculated, but this is often time-consuming. Mostly, a near optimum is calculated using heuristics. Examples of such scheduling algorithms are list scheduling and branch-and-bound scheduling. List scheduling encompasses a class of algorithms that schedule operations one at a time from a list of operations to be scheduled, using prioritisation to resolve contention for execution units. Branch-and-bound scheduling [45] considers all possible instruction orderings and selects the optimum ordering. Heuristics are used to limit the size of the search tree.

Though scheduling basic blocks causes the execution time of each basic block to be nearly optimal, this does not necessarily cause the execution time of the overall program to be nearly optimal, because the processor hesitates at each branch. The ability to look across basic-block boundaries gives the scheduler more flexibility to create a good schedule. Also, the scheduler knows about critical paths that span several basic blocks. Examples of these scheduling algorithms are trace scheduling, loop unrolling and software pipelining. A trace is a possible path through a section of code, spanning more than one basic block. The sequence of instructions in the trace is determined by assuming a particular outcome for every branch in the sequence. The effectiveness on trace scheduling depends on software knowing the likely execution trace. With trace scheduling, the execution time of likely traces is reduced at the expense of unlikely ones. Compensation code is inserted to recover from incorrect predictions. With loop unrolling, the instructions for two or more loop iterations are written explicitly. The result is a larger loop that executes half as many times. Unrolling exposes more instructions per loop iteration to the

scheduler. Software pipelining is also targeted for loop iterations and might be used in combination with loop unrolling. Basically, if the processor has n execution units, iteration i is executed sequentially on execution unit i modulo n. So the first iteration is execution on the first execution unit. After a certain time interval, the second iteration is executed simultaneously at the second execution unit. The length of the time interval is determined by the dependencies of the variables in the iteration's basic block.

Just the main scheduling algorithms for instruction-level parallelism have been mentioned here. All algorithms can be implemented for both static scheduling (during compilation, or at least before execution) and dynamic scheduling (at run-time), although some are more appropriate for static scheduling. We have made a difference between scheduling only within one basic block and scheduling beyond basic block boundaries. In reality, this distinction is not that clear; e.g. branch scheduling where a scheduler simply tries to fill stall cycles after a branch with useful instructions. The techniques mentioned might also be combined, e.g. [38]. When applying scheduling techniques for instruction-level parallelism to Multi-X, a number of observations can be made. Firstly, the APZ CP is a transaction processing system. This means little static information is available, unlike static scheduling techniques for instruction-level parallelism. A solution for this is to statically calculate all possible traces for every external signal and to base scheduling decisions on this information. As mentioned in the previous chapter, this approach has already been investigated and proved no substantial performance gains [12]. Secondly, within every function (see "Figure 1 Relationship between transactions, tasks, functions and messages"), basic blocks can be identified and a near-optimal scheduling can be calculated statically. This approach is seen as an optimisation that is beyond the scope of this thesis project. This thesis will focus on higher-level (task-level) scheduling. This is, for the time being, assumed independent of lower-level (basic block-level or instruction level) scheduling. Lastly, some scheduling techniques for instruction-level parallelism are loop transformations. As mentioned, in APZ CP code, loops are rare. This excludes techniques like loop unrolling and software pipelining. In section 3.4, "Different ways of scheduling for Multi-X", some of the ideas from scheduling for instruction-level parallelism will be used for scheduling within Multi-X.

#### 3.2.3 Task-level parallelism

Section 2.4, "Related work", shows the results of a literature survey on scheduling in task-level parallelism. Table 1 shows the different ways of scheduling in the different architectures. Since loop constructions are rare in APZ CP code, round robin scheduling as in Hydra cannot be used here. The WarpEngine proposed scheduling based on time-stamp heuristics, but this is not elaborated. The other prototypes implement scheduling as is done now in the Multi-X prototype. From this literature survey, it becomes clear that this thesis project is the first in its kind to investigate the consequences of scheduling in task-level parallelism!

#### 3.2.4 Online transaction processing

Until now, the focus of this section has been on scheduling seen from a speculative execution viewpoint. We might, however, see the APZ CP as an online transaction processing (OLTP) database system and see how close this resembles the Multi-X prototype. From this, we might find some ideas for scheduling in Multi-X.

In traditional transaction processing systems [4], transactions have four critical properties known under the acronym ACID (Atomic, Consistent, Isolated, Durable). A database state transition is *atomic* if it executes completely or not at all (commit versus rollback). A transaction is *consistent* if it preserves the internal consistency of the database. *Isolation* means that a program running transactions in a multi-user environment must behave exactly as it would in a single-user mode. This topic is also called concurrency control (the problem), serialisability (the underlying theory) or locking (the technique). *Durability* requires that the results of transactions having completed successfully must not be forgotten by the system; from its perspective, they have become part of reality. The transaction processing system guarantees atomicity, isolation and durability. Consistency is a responsibility shared between transaction programs (the user) and the transaction processing system.

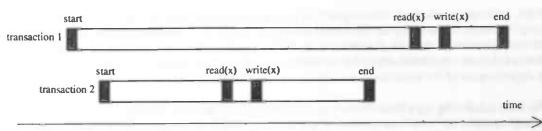

Two-phase locking mostly attains the isolation property. It says that a transaction must get all of its locks before releasing any of them. The two-phase locking theorem states that if all transactions are two-phased locked, then the execution is serialisable. This implies a basic difference with the Multi-X prototype. Let us take Figure 5 as an example where two transactions share a variable x. Let us assume (for this example) that every transaction in Multi-X consists of only one task.

Figure 5 Two transactions running in parallel

In traditional transaction processing system with two-phase locking, no collision will occur and transaction 2 will commit before transaction 1. In Multi-X, the transaction number (i.e. the transaction start time) dictates the commit order. Since the prototype prescribes in-order commit, transaction 2 will not commit until transaction 1 has committed. Locked data areas are not released until commit, which causes a data collision at the reading of x in transaction 1. Running transactions on a transaction processing system with two-phase locking results in *some* serial execution order of those transactions. It is this basic property that contradicts the Multi-X prototype, where transactions run in *the* serial execution order, dictated by the transaction number. The reason for in-order commit is the requirement for an exact similar behaviour to the serial execution on today's single-processor system. With in-order commit, this can be proved and implemented fairly easy. The Multi-X prototype might later be extended as to relax the strict commit ordering, but for now this is beyond the scope of this thesis project.

Because of this difference, scheduling techniques for online transaction processing have not been investigated more thoroughly. Two related fields of research where the ACID properties are relaxed or the transaction structure is more advanced are workflow management [13, 39] and real-time databases [1, 3, 35].

A workflow consists of many steps, where each step executes as a (traditional) transaction. Workflow management proved to focus mainly on long-lived computations resembling business processes. Often, workflow transaction models even allow human intervention. This does not correspond with the high-speed, near real-time transaction processing of the Multi-X prototype. Scheduling with time constraints in workflow management is still a relatively unexplored field of research [14]. No relevant scheduling algorithms have been found in workflow literature.

Like a traditional database system, a real-time database system must process transactions and guarantee that the database consistency is not violated. However, conventional database systems do not emphasise the notion of time constraints or deadlines for transactions. The performance goal of a system is usually expressed in terms of desired average response times rather than constraints for individual transactions. Thus, when the system makes scheduling decisions (e.g., which transaction gets a lock, which transaction is aborted), individual real-time constraints are ignored. A real-time database strives to minimise the time constraints that are violated, since it is very difficult to guarantee all time constraints. Whereas traditional database systems mostly use pessimistic concurrency (e.g. two-phase locking), real-time databases sometimes use optimistic concurrency control. Here, the execution of each transaction consists of three phases: a read phase, a validation phase and possibly a write phase, in that order. During the read phase, all writes take place on local copies. Then, if it can be established during the validation phase that the changes the transaction made will not violate serialisability with respect to all committed transactions, the local copies are made global. Only then, in the write phase, these copies become accessible to other transactions. When comparing this to the prototype of Multi-X in section 2.3, "Overview of the Multi-X prototype", it becomes clear that we might view Multi-X as an implementation of a real-time transaction processing system. However, scheduling algorithms for real-time databases base decisions mostly on transaction properties like release time (earliest time a transaction can start), deadline or estimated duration of the transaction. Only the first property is available in the APZ CP transactions. Deadlines are avoided by rerouting traffic at a higher management level.

## 3.3 Position of scheduling in the Multi-X prototype

In order to define a number of scheduling methods for Multi-X, we first need to have a better understanding of the position of scheduling in the Multi-X prototype. Taking Casavant's classification (Figure 3) as a guideline, only global scheduling will be considered in this thesis. Clearly, global scheduling in Multi-X will have to be dynamic because of the dynamic behaviour of online transaction processing. The architecture outlined in "Figure 2 Architecture of the Multi-X prototype" tends to centralised scheduling, but does not exclude distributed scheduling.

The overall goal for scheduling in Multi-X is to improve speedup (= performance) by minimising execution time (= the cost). The question is how to minimise execution time. To be able to answer this question, we need to know what parameters affect scheduling. Figure 6 gives an overview of those parameters. This set of parameters has been obtained from a number of sources, including the definition of the Multi-X prototype (see section 2.3, "Overview of the Multi-X prototype") and [10]. These are the most important parameters, but more maybe yet unknown or underestimated.

Figure 6 Relation of scheduling to other parameters in the Multi-X prototype

- The number of processors will influence scheduling performance dramatically. When measuring scheduling performance, the number of processors will have to be variable. More processors give more freedom to the scheduler and more processing capacity, but also more data collisions between the scheduled tasks. The graph speedup = f(number of processors) will therefore be a curve with a top at the optimum number of processors.

- Two collision detection algorithms have been proposed so far, as listed on "Appendix A Collision detection algorithms". More might be proposed in the future. When measuring scheduling performance, both algorithms have to be tested and compared. Since every task will eventually rollback or commit, the number of rollbacks and commits will have to be an output parameter of the scheduler. This gives also rise to four other output parameters indicating the use of a processor: idle time are those cycles spent when no task is running on a processor; wasted time are those cycles spent on running a task that is rolled back (later), including the execution of the rollback itself; executed time are those cycles spent on running a task that is committed (later), including the execution of the commit itself. In Hjalmarson's algorithm, a task might even be put on wait. The cycles spent on waiting are measured by the waiting time.

- As explained in section 2.3, "Overview of the Multi-X prototype", performing commits and rollbacks might be implemented in different ways. In this thesis project, this parameter will be static and equal to the Multi-X prototype (i.e. the original method).

- Cache behaviour and scheduling are expected to relate in two ways. First of all, scheduling itself will influence cache performance. E.g., if a specific function is often executed and consistently scheduled at the same processor, the function's code and data will remain in the cache memory and cache-hit ratio will increase. Besides this, cache dimensioning like size, number of levels and coherence protocol will influence scheduling algorithms differently. Parallel to this thesis project, another thesis project will investigate cache behaviour [53]. A cache simulator will be implemented, which might be combined to scheduling performance measurements.

- The traffic behaviour will also influence scheduling performance. E.g., short GSM calls will give other traffic characteristics than long ISDN connections. Also, traffic intensity changes in time, e.g. peaks during daytime and low intensity at night-time. Different standards exist for e.g. mobile communications. All these properties result in different traffic characteristics, which will probably need different ways of scheduling. How to define the traffic behaviour parameter is discussed more detailed in section 4.2, "Finding the right traffic data".

- The granularity of the marker field has been explained and defined in section 2.3. A more fine-grained marker field will result in less data collisions but more overhead. A more coarse-grained marker field will result in less overhead but more data collisions. In this thesis project, this parameter will be static and equal to the Multi-X prototype.

- Task granularity is defined in "Figure 1 Relationship between transactions, tasks, functions and messages". But we might also define a task as a function or an entire transaction. We will not change the definition of a task or make it variable. The current definition resembles reality best and will be easiest to implement.

## 3.4 Different ways of scheduling for Multi-X

After having examined the relevant parameters, we can conclude that we can minimise execution time by: a) minimising processor idle cycles; b) minimising the number of rollbacks, and c) minimising cache-miss ratio. In this section, a number of scheduling algorithms will be proposed aiming to minimise these costs in different ways.

When comparing different scheduling algorithms, it is interesting to know the upper and lower bound of scheduling performance, given the parameters as explained in the previous section. A lower bound will be difficult to define, but every scheduling algorithm resulting in a speedup equal to or smaller than 1.0 can be discarded. In that case, we have not gained any performance compared to an ordinary sequential execution on a single-processor system. The upper bound is equal to an *optimal scheduling*. As explained in section 3.2.2, "Instruction-level parallelism", optimal performance can be obtained by calculating the critical path of an execution trace. In order to do this, we need to know all instructions to execute in advance. How this is done, is explained in the following chapter.

The literature survey summarised in section 3.2, "Learning from other projects" merely gave some ideas, but did not result in any algorithms specifically suitable for Multi-X. Consequently, we have to go back to the basic definition of scheduling. In the first section of this chapter, we stated that scheduling decisions are made on (dynamic) properties of the objects to be executed or on (dynamic) properties of the environment in which the objects are executing. Based on this, we define three different ways of scheduling: first-come-first-serve scheduling, function-based scheduling and source-based scheduling.

- 1. First-come-first-serve scheduling means simply to send the next task to an arbitrary idle processor. This method is used at the moment in the Multi-X prototype. Scheduling decisions are neither based on any property of the tasks nor on any property of the environment. An advantage of first-come-first-serve scheduling is that it is easy to implement with little overhead. It will be easy to maximise processor load but no actions are taken to avoid rollbacks. Cache-hit ratio is not taken into account either.

- 2. From several sources in speculative execution literature, it becomes clear that avoiding data collisions is often better than curing data collisions [7, 36, 41]. Function-based scheduling is an attempt to avoid unnecessary rollbacks by examining what functions a task will execute. If two tasks use the same function, it is likely that they share a variable. This, in its turn, will cause a data collision and at least one rollback. It might be better to postpone one of the tasks. In fact, function-based scheduling focuses on the properties of the objects to be scheduled, but ignores properties of the environment. Like trace scheduling in section "Instruction-level parallelism", we will have to be able to look ahead and predict the future execution trace. At task start only the first function to be executed is known from the initiating message. This means we will have to extend the Multi-X prototype with control speculation (e.g. branch predictors), since currently only data speculation is supported. The prediction mechanism will have to be implemented in software, since we assume no hardware support for task-level parallelism. This will increase scheduling overhead. Maximising processor load will be more difficult for function-based scheduling than for first-come-first-serve scheduling. However, the number of rollbacks will decrease and the assignment of tasks to processors might be done carefully in order to increase cache-hit ratio. The function-based scheduling as defined here is a division of function in time. Another solution is to divide functions in space; i.e. by assigning every function to one specific processor. Space-division is hard in our case, since we defined the task granularity as a number of functions.

- 3. With source-based scheduling, we focus on the properties of the environment but ignore the properties of the objects to be scheduled. The idea is to base scheduling decisions on the origin of the external messages

(see "Figure 1 Relationship between transactions, tasks, functions and messages"). All external messages originate from some remote processor. Every remote processor serves a number of devices, and every device serves a number of subscribers. Consequently, source-based scheduling is an attempt to map individual subscribers to individual processors. Since every subscriber has its own data, cache-hit ratio will improve. Since different subscribers will use different services in time, i.e. functions, source-based scheduling is also expected to decrease the number of rollbacks. Balancing and maximising processor load is assumed not to raise any difficulties. If it does, higher-level traffic management might solve this by dividing load more evenly from the different remote processors.

The three different ways of scheduling proposed here are by no means exhaustive; they just indicate three basic solutions. In fact, these are three extremes that give a broad understanding of scheduling behaviour in Multi-X. The best solution for Multi-X will probably be some combination of the scheduling algorithms mentioned here.

Even if the best scheduling algorithm can be defined for a particular set of parameters (see Figure 6), this scheduling algorithm will probably not be best if some parameter changes. This leads to the notion of an adaptive scheduling algorithm [66]. We define a scheduling algorithm to be adaptive if 'the rule base for making scheduling decisions is not fixed, but changes with the dynamic behaviour of the environment'. The environment does not only include the set of parameters as in Figure 6, but also output parameters of the current scheduling (e.g. number of rollbacks or waiting time). Note that this definition differs from the definition of dynamic scheduling in Casavant's classification (Figure 3). A dynamic scheduling algorithm might very well have a fixed rule base. One way to implement an adaptive scheduling algorithm is a two-level approach. A number of nonadaptive scheduling algorithms are defined, all optimised for a specific environment. At a higher level, another algorithm classifies the environment (at run-time) and selects the best suiting non-adaptive algorithm. The classification algorithm might be implemented using techniques from the field of computational intelligence, e.g. fuzzy logic as in [11] or neural networks. One step further is to let the high-level algorithm not only classify the environment, but also produce a scheduling algorithm. This might be solved using neural networks [46, 60] or even genetic algorithms [74]. For now, an adaptive scheduling algorithm is remote future. This thesis will focus on the non-adaptive approaches mentioned above. Based on that knowledge, an adaptive algorithm might be defined in a later stage. The next chapter will summarise the different ways of scheduling and will describe how to investigate these.

# 4 Measuring scheduling performance

The previous chapter defined four ways of scheduling to investigate: three practical algorithms (first-come-first-serve scheduling, function-based scheduling and source-based scheduling) and one theoretical algorithm (optimal scheduling). The latter will give us an upper bound on scheduling performance. As output parameters for the scheduling algorithm we defined the number of commits, the number of rollbacks and for every processor: executed time, wasted time, waiting time and idle time. The cache-hit ratio will indirectly be an output parameter if the scheduling algorithm can, in some way, be linked to the cache simulator. Performance, expressed in speedup, can be deduced from these output parameters.

In the first section of this chapter, three ways of measuring performance parameters are compared. One way, implementing a simulator, is chosen for measuring performance in this thesis project. The succeeding chapter defines the data to be used as input for the simulator and describes how this data is obtained. Some statistics on the input data are presented. Section 4.3 describes the model of the prototype used as a basis for the simulator. Most issues have already been highlighted in previous chapters. Here, we merely present some important implementation details. Performance of optimum scheduling, as a theoretical approach, cannot be measured using the simulator. The last section of this chapter explains how optimal scheduling will be calculated.

## 4.1 How to measure performance parameters

Now we know what to investigate, we can decide how to investigate scheduling performance. Basically, we have three possibilities: implementing the scheduling algorithms in the Multi-X prototype, defining a mathematical or statistical model or simulating the Multi-X prototype.